概述

VP@rcvr,Virtual Probe @ Receiver是力科高档信号完整性剖析软件包Eye Doctor II中的一种数学运算功用,其规划意图是补偿由于端接不匹配形成的反射问题。它的一个很大长处是能够运用咱们了解的端接模型,相比之下,咱们知道其它的一些去嵌东西则需求DUT的S参数,而这种端接的S参数 是很难取得的。

波形丈量的困难

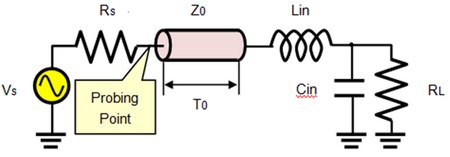

由于PCB布线密度越来越大,在物理尺度上几乎不可能在抱负的方位上如接纳机的端接点直接用探头来勘探。这种情况下,必须在端接点之前测验信号,如图1所示。可是,这个测验点可能会遭到端接反射的影响。

图1 实践电路中一般的测验点方位示意图

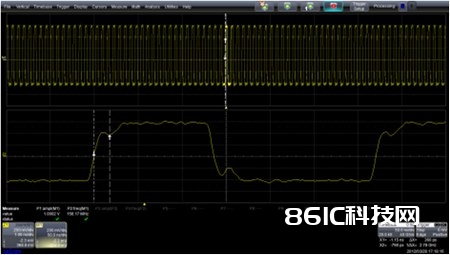

图2便是这种反射带来影响的一个比如。 这个信号是156MHz的时钟,在接近接纳机芯片的过孔进行勘探。明显,该波形在间隔边缘360ps的方位有反射存在。

对反射进行补偿的东西

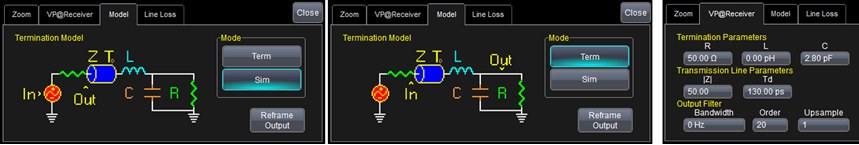

为了对反射进行补偿,咱们能够运用去嵌/仿真东西,可是这些东西一般都需求DUT的S参数。力科公司高档信号完整性剖析软件包Eye Doctor II供给的VP@rcvr (接纳端虚拟勘探) 功用能够十分方便地运用图3中咱们所了解的端接模型对这种反射进行补偿。

它有两个形式: “Simulation” 和“Termination”。在“Termination”形式下仿真端接点的信号波形以补偿根据不抱负的接纳端端接电路带来的反射。“Simulation” 形式可用于验证“Termination”形式的仿真作用。

根据力科示波器的信号源仿真东西JitterSim

为了装备端接模型并进行验证,力科的高档串行数据剖析软件包SDA II供给的JitterSim东西能够十分方便地仿真发射机信号。在本例中, JitterSim发生一个156.17MHz的时钟信号,上升时刻为250ps, 占空比为40%,幅值为2V,如图4中的F1所示。

图4:运用JitterSim仿真作为信号源仿真发送端信号

验证端接模型

为了验证补偿的端接模型,咱们能够运用VP@rcvr 的“Simulation” 形式和JitterSim发生的抱负的发射端信号。在这个使用中,F2被设置为VP@rcvr中图5所示的“Simulated” 形式。

信号通路假设是50 ohm体系,Td设置为130ps, 它是实践信号发生反射的时刻的一半。F2波形是根据端接模型的勘探点的仿真成果波形。假如F2和实践丈量到的信号形状十分共同,表明端接模型适合于补偿实践的端接。在本例中,运用%&&&&&%C=2.8pF,F2和图6中的M1波形十分共同。

图6:运用JitterSim和VP@rcvr仿真的成果和实践丈量的信号比较

补偿反射

现在,端接模型能够用于VP@rcvr中的“Termination”形式的反射补偿了!将F2的源由 F1改为M1,M1是实践丈量到的信号。将VP@rcvr中的“Simulation” 形式改为 “Termination”,那么现在 F2表明的便是仿真到的端接点的信号,如图7所示。

图7: 运用VP@rcvr的“Termination”形式在端接点仿真的信号

F2现在是洁净的时钟信号,没有反射。这个波形可用于对接纳端的信号进行准确的定位。