最近在看关于Silicon Labs的C8051F347的某个驱动中,关于SPI部分初始化的代码,看到其关于SPI的设置为CPOL=1,CPHA=0,关于CPOL及CPHA的意义不了解,想要搞懂,这两个参数到底是什么意思,以及为何要这么设置。所以才去找了SPI的极性和相位的相关材料,收拾如下。

【SPI基础知识简介】

设备与设备之间经过某种硬件接口通讯,现在存在很多种接口,SPI接口是其间的一种。

SPI平分Master主设备和Slave从设备,数据发送都是由Master操控。

一个master能够接一个或多个slave。

常见用法是一个Master接一个slave,只需要4根线:

SCLK:Serial Clock,(串行)时钟

MISO:Master In Slave Out,主设备输入,从设备输出

MOSI:Master Out

SS:

SPI因为接口相对简略(只需要4根线),用处算是比较广泛,首要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

即一个SPI的Master经过SPI与一个从设备,即上述的那些Flash,ADC等,进行通讯。

而主从设备之间经过SPI进行通讯,首要要确保两者之间时钟SCLK要共同,相互要商议好了,要匹配,不然,就无法正常通讯了,即确保时序上的共同才可正常讯。

而这儿的SPI中的时钟和相位,指的便是SCLk时钟的特性,即确保主从设备两者的时钟的特性共同了,以确保两者能够正常完成SPI通讯。

【SPI相关的缩写或说法】

先简略说一下,关于SPI中一些常见的说法:

SPI的极性Polarity和相位Phase,最常见的写法是CPOL和CPHA,不过也有一些其他写法,简略总结如下:

(1) CKPOL (Clock Polarity) = CPOL = POL = Polarity =

(2) CKPHA (Clock Phase)

(3) SCK=SCLK=SPI的时钟

(4) Edge=边缘,即时钟电平改变的时间,即上升沿(rising edge)或许下降沿(falling edge)

关于一个时钟周期内,有两个edge,别离称为:

Leading edge=前一个边缘=第一个边缘,关于开端电压是1,那么便是1变成0的时分,关于开端电压是0,那么便是0变成1的时分;

Trailing edge=后一个边缘=第二个边缘,关于开端电压是1,那么便是0变成1的时分(即在第一次1变成0之后,才可能有后边的0变成1),关于开端电压是0,那么便是1变成0的时分;

本文选用如下用法:

极性=CPOL

相位=CPHA

SCLK=时钟

第一个边缘和第二个边缘

【SPI的相位和极性】

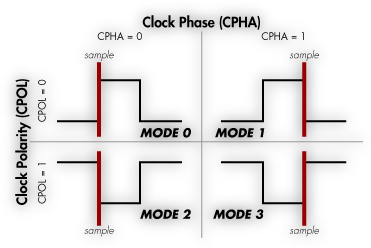

CPOL和CPHA,别离都能够是0或时1,对应的四种组合便是:

| Mode 0 | CPOL=0, CPHA=0 |

| Mode 1 | CPOL=0, CPHA=1 |

| Mode 2 | CPOL=1, CPHA=0 |

| Mode 3 | CPOL=1, CPHA=1 |

独自看这张图,确实很难理解具体意义,所以下面会有更具体的解说。

【

先说什么是SCLK时钟的闲暇时间,其便是当SCLK在数发送8个bit比特数据之前和之后的状况,于此对应的,SCLK在发送数据的时分,便是正常的作业的时分,有用active的时间了。

先说英文,其精简解说为:Clock Polarity = IDLE state of SCK。

再用中文详解:

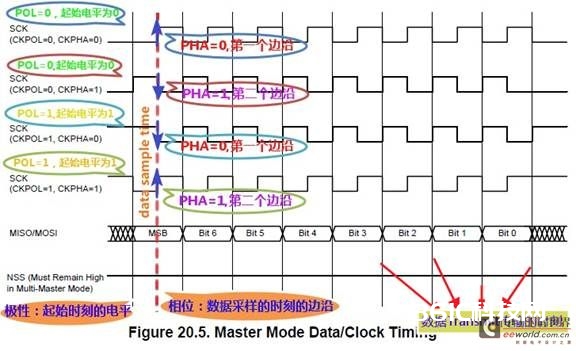

SPI的CPOL,表明当SCLK闲暇idle的时分,其电平的值是低电平0仍是高电平1:

CPOL=0,时钟闲暇idle时分的电平是低电平,所以当SCLK有用的时分,便是高电平,便是所谓的active-high;

CPOL=1,时钟闲暇idle时分的电平是高电平,所以当SCLK有用的时分,便是低电平,便是所谓的active-low;

【

首要阐明一点,capture strobe = latch = read = sample,都是表明数据采样,数据有用的时间。

相位,对应着数据采样是在第几个边缘(edge),是第一个边缘仍是第二个边缘,0对应着第一个边缘,1对应着第二个边缘。

关于:

CPHA=0,表明第一个边缘:

关于CPOL=0,idle时分的是低电平,第一个边缘便是从低变到高,所所以上升沿;

关于CPOL=1,idle时分的是高电平,第一个边缘便是从高变到低,所所以下降沿;

CPHA=1,表明第二个边缘:

关于CPOL=0,idle时分的是低电平,第二个边缘便是从高变到低,所所以下降沿;

关于CPOL=1,idle时分的是高电平,第一个边缘便是从低变到高,所所以上升沿;

用图文方式表明,愈加简单看懂:

此处,再多解说一下可能会遇到的CKP和CKE,其是Microchip的P%&&&&&%系列芯片中的说法。

(1)CKP是Clock Polarity Select,便是极性=CPOL:

CKP,尽管姓名和CPOL不相同,可是都是指时钟相位的挑选,界说也相同:

CKP: Clock Polarity Select bit

1 = Idle state for clock (CK) is a high level

0 = Idle state for clock (CK) is a low level

所以不多解说。

(2)CKE是Clock Edge Select,便是相位=CPHA:

CKE: SPI Clock Edge Select bit

1 = Transmit occurs on transition from active to Idle clock state

0 = Transmit occurs on transition from Idle to active clock state

意思是

1 =(数据)传输发生在时钟从有用状况转到闲暇状况的那一时间

0 =(数据)传输发生在时钟从闲暇状况转到有用状况的那一时间

其间,数据传输的时间,即图中标出的“数据transmit传输的时间”,很明显,该时间是一个时钟和下一个时钟之间接壤的当地,对应的不论是上升沿仍是下降沿,都与咱们前面说到的CPHA=数据采样的时间,的边缘方向所相反。

所以,此处的CKE,正好与CPHA相反。