0 导言

RS232接口是1970年由美国电子工业协会(EIA)联合贝尔体系、调制解调器厂家及计算机终端生产厂家一起拟定的用于串行通讯的规范。它的全名是“数据终端设备(DTE)和数据通讯设备(DCE)之间串行二进制数据交流接口技术规范”。该规范规则选用一个25个脚的DB25连接器,对连接器的每个引脚的信号内容加以规则,还对各种信号的电平加以规则。跟着设备的不断改进,呈现了替代DB25的DB9接口,现在都把RS 232接口叫做DB9。RS 232接口是最常见的一种串行通讯接口,一般PC机一般都具有此类接口,其最高通讯速率(波特率)为115.2 Kb/s。选用9 600b/s进行数据传输交流的使用较多。经过FPGA完结其时序电路,首要完结发送和接纳两部分逻辑电路的规划。

1 发送逻辑电路的规划

1.1 时序近似

RS 232接口可选的波特率如9 600b/s,115.2 Kb/s同等11.059 2 MHz的时钟有着整数倍的联系,但通常情况下供给FPGA的时钟大多选用频率为40~80 MHz,同11.059 2 MHz之间存在必定的时序差错。

例如一个由1个开始位,8个数据位,1个中止位组成,假定串行信号的波特率为9 600b/s,则每个位的时序时间为:

104 166.666 666 666 666 666 666 666 666 67 ns

相当于80 MHz计数器计数到:

8 333.333 333 333 333 333 333 333 333 333 3舍去小数部分。

由80 MHz驱动的计数器发生时序时每个字符差错为4.166 666 666 666 666 666 666 666 666 666 7 ns。这样由10个字符组成的一次发射时序差错约为41.7 ns小于1/1 000能够忽略不计。

1.2 发送时序规划

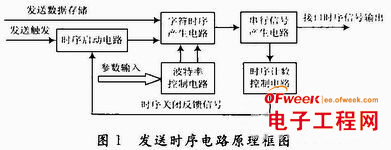

RS 232接口的时序电路由发动电路、字符产牛电路、同步时钟发生电路。波特率操控电路,和时序封闭电路组成。发送时序电路原理框图如图1所示。

1.3 发送电路原理描绘

以波特率为9 600b/s的时序为例,在发送数据之前,体系微处理器将相应波特率参数锁存在FPGA内部的波特率操控电路的寄存器内(由触发器构建),使每次输出的字符同步信号的周期为104.167μs(对应波特率9 600b/s)。

当体系宣布发送发动信号时,字符时序电路以每个字符104.167μs的速率在预发射数据的逻辑电平操控之下输出时序信号,一起在时序中刺进中止位和开始位字符信号。

在完结上述发送时序的进程中,时序计数操控电路会检测发送时序的作业状况,当检测每次时序的中止位完结输出后,时序计数操控电路会宣布时序封闭反应信号,使电路回复到预发射的初始作业状况,并等候处理器再次触发时序电路和对数据参数的重置。

2 接纳逻辑电路的规划

2.1 接纳时序规划

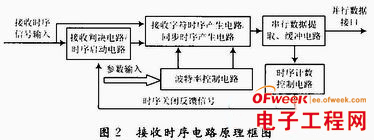

接纳时序电路原理框图如图2所示。

2.2 接纳电路原理描绘

以波特率为9 600b/s的时序为例,在接纳数据之前体系微处理器将相应波特率参数锁存在FPGA内部的波特率操控电路的寄存器内(由触发器构建),使每次输出的字符位同步信号的周期为104.167 μs(对应波特率9 600b/s)。字符位同步信号是接纳电路存储接纳数据逻辑状况的要害。作为同步时钟信号,该信号可驱动接纳到的串行数据电平输入移位寄存器内并锁存。

当体系接纳到一帧串行信号时,首先要判别是否是新的一帧数据,接纳判定电路经过对输入串行信号的开始位字符脉宽进行判决,依照RS 232接口通讯协议在某一特性波特率下,一帧信号的开始是必定脉宽的负脉冲。经过计数器能够检测到负脉冲的开始时间和脉冲宽度,当脉冲宽度抵达某一数值时发动接纳时序。

接纳时序电路会经过被记载下的接纳信号的精确抵达时间,推算出每个串行数据位对应的时序时间,然后输出对应每个位中心时间的字符位同步信号(脉冲)作为接纳移位寄存器的同步时钟信号驱动移位寄存器对接纳数据电平的记载。

被锁存的数据经过并行总线被体系微处理器提取。这一进程能够经过对处理器的中止完结,但需求接纳时序电路在完结数据接纳后当即发生一个中止信号,告诉处理器提取接纳数据。

接纳时序计数器会对接纳时序时间进行检测,当接纳时序抵达完毕时间时,其输出的时序封闭反应信号会使接纳电路康复到初始作业电路,等候下一帧数据的抵达。

3 定论

经过FPGA完结RS 232接口时序逻辑电路,已经在工程实践进程中完结了接口规范规则的悉数功用。能够以为,经过FPGA的逻辑电路规划能够彻底替代专用芯片。介于FPGA的可塑性和灵活性,能够经过相应逻辑电路规划完结包含以太网,USB、RS 485等常见的数据接口。