可装备处理器标志着第四代微处理器规划的开端,这种技能愈加合适片上体系SOC的规划。每一代处理器继续大约十年时刻,每个年代的处理器合适其时那个时期的需求。大约在二十世纪七十年代呈现了第一代处理器,这个时期的处理器规划仅仅简略地寻求功用,从4位处理器到前期的16位和32位微处理器。这种功用的进步奠定了二十世纪八十年代个人计算机PC和作业站的根底。个人计算机和作业站的添加使得微处理器规划进入了二十世纪八十年代的第二代微处理器研发时期。精简指令集RISC规划年代发生在二十世纪九十年代。在这个时期,即便像X86这样坚决的杂乱指令集CISC处理器也假装成精简指令集RISC体系结构。在开端的这三代处理器的生长和开展过程中,微处理器规划专家将处理器规划成固定的、单个的和可重用的模块。可是,在二十世纪九十年代跟着专用集成电路ASIC和片上体系SOC制作技能的开展为微处理器规划进入第四代(即后RISC、可装备处理器)打下了坚实的根底。

当今的体系开发东西现已十分先进,完全能够答应规划人员依据详细的使用方针使命来定制微处理器核。处理器定制能够在十分短的时刻内,乃至是几分钟就能够依据详细使用完结片上体系处理器核的规划。由于依据详细使命来定制处理器的速度十分快,因而可装备处理器能够具有十分优异的高功用来构建片上体系的规划,而且常常用于快速树立一些功用模块,而这些功用模块假如选用人工RTL办法规划的话,则或许需求几个月的时刻。正是由于可装备处理器技能的高功用和快速开发才能,使得许多终究产品在多个可装备处理器核的根底上完结了片上体系SOC(多处理器片上体系SOC或许简写为MPSOC)。这些终究产品的规模从最大和最小的网络路由器一向到比如便携式摄像机、打印机和低成本视频游戏机等消费类电子产品。

两种最新的开发技能现已嵌入到可装备处理器乃至片上体系SOC规划中,即全自动化的、专用指令集定制技能和对处理器内部履行部件的多口拜访技能。前者答应片上体系规划人员愈加专心体系体系结构方面的问题,而经过依靠自动化规划东西来完结某些单一功用模块以到达功用方面的方针。后者则永久克服了曾经那种存在已久的总线瓶颈问题,而这种总线瓶颈问题从1971年第一个微处理器呈现以来就一向阻止微处理器功用的进步。

自动化处理器定制

十多年来,硬件规划人员一向在尽力用C或许C++对体系进行描绘从而转换成有用的硬件。开端的体系阐明通常是用C或许C++写成的,由于选用这些高档言语描绘的体系能够在廉价的PC上进行履行和点评。但是,即便是廉价的PC也不合适许多嵌入式体系的规划,尤其是在消费电子范畴,由于其功耗太大。因而,规划人员开端期望找到一种东西来将用C或许C++写成的体系描绘转换成硬件。

许多像“行为归纳”、“C言语硬件归纳”和“ESL”等词汇描绘的规划办法都有一些缺点,由于它们都是企图处理在本质上很杂乱的问题:用时序可履行言语写成的体系描绘转换成并行互操作和非可编程的硬件模块。

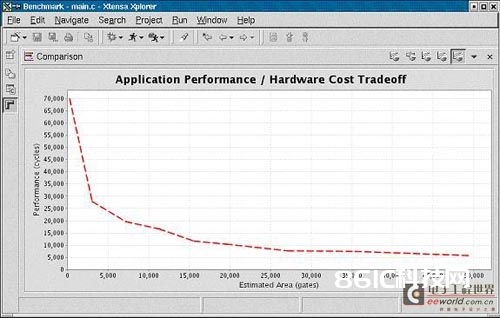

Tensilica的XPRES编译器选用一种愈加简略、愈加直接的办法来处理这一规划问题。XPRES编译器不是企图从头开端进行与使用相关的硬件规划,而是从一个完好的功用处理器核开端规划,然后以添加硬件履行部件和相应的机器指令的办法来添加硬件,以加快处理器上方针使用程序的履行速度。因而,XPRES编译器从一个正在作业的硬件(Xtensa微处理器核)开端规划,一起使得方针程序代码运行得更快。这种查找的结果是完结一个微处理器的装备,此装备有一个功用/硬件开支的特性曲线,如图1所示。

图1: XPRES编译器为规划者供给一系列微处理器装备。跟着硅片面积的添加也使得与使用相关的体系功用得到进步。

功用优化的三种技能途径

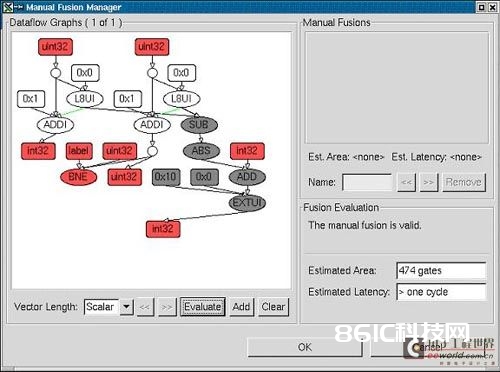

XPRES编译器选用三种技能来树立优化的Xtensa处理器装备:操作数交融、单指令流多数据流SIMD(向量化)和FLIX(可变长度指令扩展)。操作数交融技能记载程序循环语句中简略操作呈现的频度。XPRES编译器将这些指令序列合并成一条增强型指令,这种增强型指令经过削减循环内部的指令条数来加快程序代码的履行。图2表明由XPRES编译器发生的数据流操作,图顶用灰色表明出交融操作。

图2:由XPRES编译器发生的数据流图表明出一系列交融操作。当减法操作、取绝对值操作、加法操作和位域抽取操作交融成一条新的指令后,由XPRES编译器进行评价需求添加474个逻辑门。