摘要:针对机械设备运转中的振荡监控,规划振荡信号收集体系,提出了一种根据FPGA的振荡信号收集体系的规划方案。要点论述了体系硬件结构组成、信号调度电路和数据收集模块的规划,一起对A/D采样的操控逻辑进行了评论。经试验验证标明,该体系可到达采样率10 K每秒、收集精度16位,能够满意实时性和精度要求。

跟着出产机械、运送机械或工程结构向着高速、高效、高精度和大型化开展,机械设备的任何部件呈现毛病都可能下降加工精度,带来较大的经济损失,乃至危及人身安全。机械部件的振荡状况监测已成为出产中的一个必不可少的环节,并对相应机械部件进行前期的毛病猜测。文中选用FPGA为中心开发振荡信号收集体系,对数据收集模块及通讯模块进行了同步规划。

1 总体规划

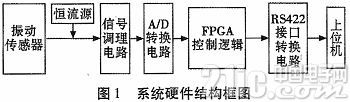

振荡信号收集体系以FPGA芯片为中心,通过A/D转化芯片收集振荡信号,然后通过RS-422串行总线接口将收集的数据传输给上位机,在毛病确诊软件以作出相应的确诊处理。振荡信号收集体系的硬件依照功用模块能够划分为信号调度电路、A/D转化电路、FPGA操控逻辑和RS-422接口转化电路,体系硬件结构如图1所示。

体系硬件各个功用模块的效果如下:

1)信号调度电路:信号调度电路首要对由集成电路压

电式(Integrated Circuit Piezoelectricity,ICP)加速度传感器收集到的振荡信号进行调度驱动、扩大和抗混叠滤波处理,使模数转化器(Analog to Digital Converter ADC)芯片能够获取该振荡信号,并作出进一步处理作业。

2)A/D转化电路:A/D转化电路将通过信号调度的信号进行模/数转化,并将转化成果传送至FPGA进行数据收集,此功用电路决议了整个体系的分辨率和收集精度。

3)FPGA操控逻辑:FPGA芯片是该主控模块的中心部分,操控振荡信号的收集和数据传输,此功用电路操控着体系的采样周期。

4)RS422接口转化电路:将A/D转化后的数字信号,通过RS422总线传输到上位机。

2 硬件电路规划

2.1 恒流源电路

体系选用ICP%&&&&&%压电式加速度传感器检测被测设备的振荡信号,它将传统压电加速度传感器和扩大器集于一体,供电和信号输出共用同一根电缆,通过恒流源为其供电,输出信号通过信号调度电路后衔接单片机进行测验,使收集体系得到了简化,削减电缆的数量,一起省去了电荷扩大器,下降了本钱。

ICP传感器所需的供电电源有必要能够供给18~30 V的直流电压以及2~20 mA的恒定电流。因为传感器共用电源线与信号输出线,所以它的输出信号会包括一个8~14 V的直流偏置电压,通过去耦电容滤除信号中的直流重量。

本体系选用TI公司的三端可调恒流源器材LM334芯片。LM334为单片三端可调恒流源,实践运用中,改动衔接电阻就可构成不必独立电源的两头抱负电流浮置源,改动R能够改动恒流源的电流值,其公式为:

体系中设置为LM334的作业电压28 V,电阻R标称值33 Ω,输出电流为2 mA。

2.2 信号调度模块的规划

2.2.1 阻隔、扩大电路规划

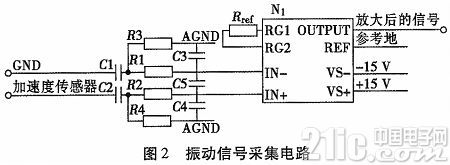

%&&&&&%P加速度传感器输出信号包括有直流偏置电压,电路规划隔直电容C1和C2滤除此直流重量,然后选用精细外表运算扩大器芯片完结对模拟信号的扩大处理,通过调理外部份额电阻可完结增益从1至10 000之间的恣意挑选。 阻隔、扩大电路的原理图如图2所示。

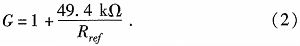

N1为精细外表运算扩大器,其增益值根据下式可核算得出:

式中:G为电压扩大增益;Rref为份额参阅电阻,单位Ω。

现阶段取Rref开路,即Rref=∞,核算可知G=1。

R1、R2为输入端匹配电阻,标称值4.7 kΩ。

R3、R4为开路接地电阻,标称值1 MΩ。

C1、C2为输入端隔直电容,标称值0.1μF,额外电压值50 V。通过C1,C2和R3,R4构成的高通电路,-3 dB到频点是15.92 Hz,对信号进行隔直处理,一起不影响收集信号。

C3、C4、C5为精细外表运算扩大器输入端的滤波电容,标称值为0.001μF、0.01μF、0.001μF,与R1、R2构成低通电路,对共模信号的-3 dB到频点是33.87 kHz,关于差模信号的-3 dB到频点是1 610 Hz,有用的滤除进入收集电路的搅扰信号。

2.2.2 抗混滤波电路规划

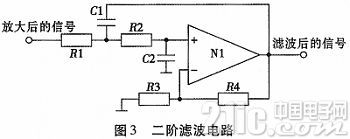

通过扩大处理后的振荡信号会稠浊有高频搅扰信号,这些高频信号就会发生频率混叠现象,形成收集体系的精度下降。

抗混滤波电路选用二阶压控电压源低通滤波电路,滤波器的截止频率则由电阻R1、R2和%&&&&&%C1、C2操控。二阶低通滤波电路的原理图如图3所示。

滤波电路规划参数如下:

R1=R2=15 kΩ,R3=R4=10 kΩ,C1=C2=10nF;

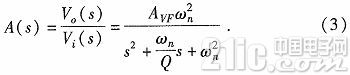

二阶低通滤波电路的传递函数为:

式中:A(s)为开环增益;Q为等效品质因数;ωn为电路的特征角频率s。

其间Avf=1+R3/R4=2,Q=1/(3-Avf)=1>0,故A(s)的极点悉数位于左半s平面,电路不会发生自激震动。

另一方面,由滤波电路传递函数可得幅频呼应表达式为:

能够核算出,其在ω/ωn=10时,幅频特性曲线有-40 dB的衰减,电路的幅频呼应具有较好的低通特性,滤波器截止频率f=1/2πRC≈1 062 Hz。

2.3 数据收集模块的规划

数据收集模块首要环绕A/D转化芯片打开规划,体系选用单通道的16位A/D转化芯片进行采样,采样频率最高别离可达100 ksps。方针采样的振荡信号的频率一般为低频信号,规划收集体系的检测5 kHz频率范围内的振荡信号,依照香农采样定理,A/D转化芯片的收集速率应不小于10 k每秒,100 ksps的A/D转化芯片完全能够满意本体系需求。

因为A/D转化芯片输出电平为5 V的TTL电平,需求装备电平转化芯片,将5 V电平转化为3.3 V电平,再送入现场可编程门阵列(Field Programmable Gate Arrays,FPGA),完结对收集电路中A/D转化芯片的时序操控。

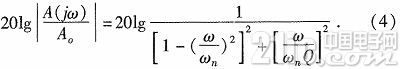

A/D转化公式:A/D芯片收集到的数值为0~0xFFFF的16位二进制数,对应-10 V~+10 V的电压,电压转化核算公式如下:

2.4 通讯模块的规划

RS-422驱动电路由UART协议、电平转化和接口电路组成,其间协议转化由可编程逻辑完结。串行接口数据格式为:1个开端位,8个数据位,奇校验位,1个中止位,作业频率规划在115 200 bps。FPGA芯片将收集到的AD转化后数据转发到RS-422总线。因为AD收集芯片为16 bit,所以在设置先发数据的高8 bit,再发送数据的低8 bit。

3 可编程逻辑规划

3.1 可编程逻辑功用规划

体系选用Xilinx公司的Spartan系列芯片,此系列具有功用优秀、性价比高、非易失性等特色,扩展了片上flash存储器,用于FPGA的装备和非易失性数据的存储,具有足够的资源满意收集体系的逻辑功用需求。可编程逻辑选用模块化的规划思维,规划AD收集模块和UART协议模块。

3.1.1 AD收集模块

FPGA芯片操控A/D转化芯片RC信号为低电平,AD芯片发动转化作业,一起BUSY信号输出低电平,转化完结后AD芯片BUSY信号重置高电平,AD芯片数据输出端口输出有用数据。FPGA检测到BUSY信号,将AD芯片转化后的数据存入UART发送寄存器中。

3.1.2 UART协议模块

UART协议模块选用的是串口通讯协议软核,其规划特色是:

1)波特率为9 600 bps~115.2 kbps可通过软件编程;

2)内建128字节接纳FIFO和128字节发送FIFO;

3)数据长度、中止位长度、奇偶校验可通过软件进行编程;

4)核算公式:波特率=外部时钟(14.745 6 MHz)/(16×分频因子)。

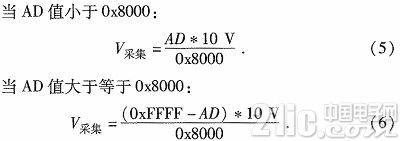

3.2 体系功用逻辑规划

收集体系的操控规划为周期主动收集,一次采样进程如下:首要发动A/D转化器,然后判别BUSY信号转化是否完毕,A/D转化完毕后FPGA读取A/D转化成果,并直接存入UART发送寄存器,然后等候延时到下一周期,并开端第2次收集,主动完结振荡信号的收集。FPGA的主动操控流程如图4所示。

体系规划采样周期为200 us,远大于A/D转化芯片的转化时刻,决议了体系的采样速率5 kHz,可满意大多数机械部件振荡信号的收集要求。采样周期操控由FPGA运用的时钟计数决议,此体系运用的时钟为10 MHz,体系的周期差错来源于晶振自身的差错,体系运用的晶振初始频率一温度差错为50 PPM,具有极小的时钟差错。

4 体系功用验证

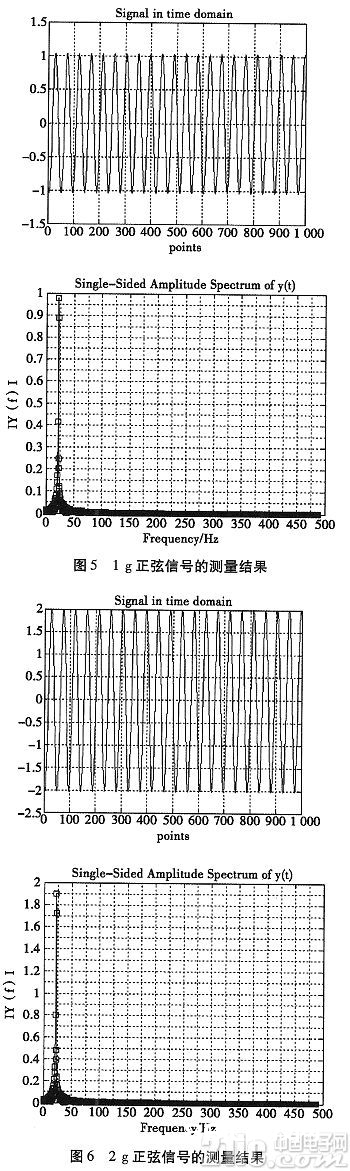

为了验证振荡信号收集体系的各项功用,本研讨选用由振荡台输出的正弦信号作为体系的输入鼓励,由本文规划的收集体系对该振荡信号进行收集,然后查验体系收集功用的准确性。试验中用到的设备状况如下:运用随机振荡台,施加21.5 Hz正弦振荡鼓励信号,幅值别离为1 g和2 g两种鼓励,运用振荡传感器精度为104 mV/g,丈量成果为图5和图6所示。

由图能够看出,信号的幅值挨近鼓励值,与输入的正弦鼓励信号根本共同,进行频率剖析,进行FFT转化后频率为21.5 Hz,与输入鼓励信号的频率共同。试验成果标明,该振荡信号收集功用正确。

5 定论

本文提出的FPGA的振荡信号收集体系具有硬件组成少,可在不需求中央处理器即可完结数据的主动收集,且具有并行可扩展性,功用移植性好,一起具有较高的采样周期和精度,能够满意大多数工业与航空领域中振荡收集的要求。