时钟扩展对运用赛灵思Vivado规划套件的工程师来说是一个很大的应战,但不是一个不可逾越的妨碍。

跟着越来越多的赛灵思用户开端运用Vivado®规划套件,部分用户对未扩展时钟表明困惑。那么什么是未扩展时钟呢?他们是怎么进行相关和计时的?应对未扩展时钟的规范办法又是什么呢?下面让咱们来具体讨论一下这个问题,重点是讨论保证规划人员运用正确的同步技能安全地穿越未扩展时钟之间的跨时钟域(clock domain crossing)的办法。

跟着Vivado东西的推出,赛灵思现在可以支撑选用业界规范Synopsys规划束缚(SDC)格局的时序束缚。这是ISE规划套件东西处理时序办法上的严重改变。Vivado套件最底子的差异在于一切时钟在默许条件下都互相相关。这样在ISE中处于无束缚状况的时序途径在Vivado规划套件中则处于受束缚状况。假如两个时钟之间不存在周期性联系,这种束缚会形成十分严厉的时序要求。

未扩展时钟是指在1,000个时钟周期内与另一个时钟之间不存在周期性联系的时钟。Vivado BFT 内核典范规划便是表现未扩展时钟作业办法的杰出途径。

建议和捕获

时序途径从建议事情开端,由捕获事情停止。建议事情产生在同步单元的时钟从非作业状况转入作业状况的时分。捕获事情产生在下流的或许担任捕获的同步单元的时钟从非作业状况转入作业状况的时分。从建议事情到捕获事情之间所需的时刻被称为“途径要求”,它代表自事情建议后到捕获单元引脚处呈现有用数据之间所需的时刻。

假如建议时钟和捕获时钟一起坐落同一物理时钟网中,途径要求仅指时钟周期。以250MHz时钟为例,假如建议单元和捕获单元的作业沿相同(上升沿对上升沿或下降沿对下降沿),那么建议事情和捕获事情之间的时刻距离则刚好为4纳秒。假如建议单元和捕获单元的作业沿不同,途径就必须按一半的时钟频率进行时刻核算。这便是时钟的上升沿对下降沿或下降沿对上升沿转化的状况,对一个250MHz的时钟来说,对应的便是2纳秒的途径要求。

在时钟源(source clock)和时钟方针端(destination clock)非同一个时钟的状况下,时序问题就变得愈加杂乱。具有不一起钟源和时钟方针端的时序途径被称为跨时钟域(CDC)途径。

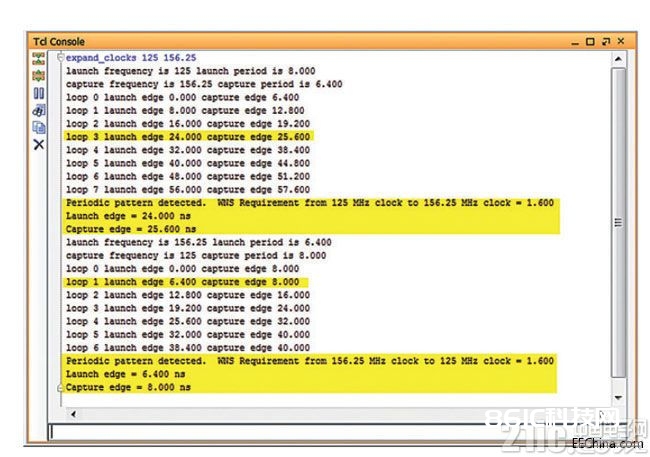

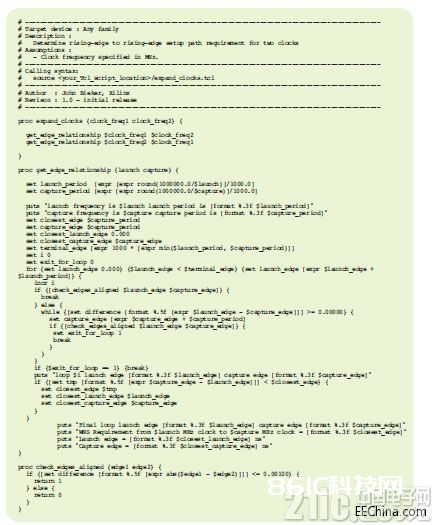

图1:扩展时钟的TCL脚本

假如建议时钟和捕获时钟之间的相位联系不知道,就无法核算途径要求。由于不承认相位联系,则无法精确承认途径时序。不安全时钟在Vivado规划套件生成的时钟交互陈述中会杰出显现。在建议时钟和捕获时钟之间的相位联系已知的状况下,只需两个时钟之间存在周期性联系,就可以用数学办法推导出途径要求。用于判别给定建议时钟和捕获时钟之间最低途径要求的办法称为时钟扩展。不过承认两个时钟之间是否存在周期性联系需求用实践束缚加以束缚,由于一般状况下两个不一起钟之间不存在一起的周期性特征。Vivado规划套件运用的实践束缚条件是1,000个时钟周期,以两个时钟中较小的时钟周期为丈量规范。假如在扩展两个时钟到超越1,000个时钟周期后没呈现周期性联系,那么这两个时钟就被称为“未扩展”时钟。Vivado规划套件对两个未扩展时钟之间的途径要求为建议时钟和捕获时钟相邻作业沿之间相隔的最少时刻。但需求留意的是对超越1,000个时钟周期的状况有愈加严厉的途径要求,这便是Vivado规划套件将这种类型的两个时钟之间的联系称之为未扩展的原因。

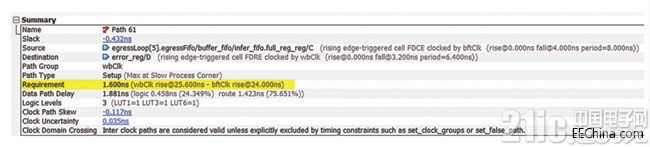

图2:125MHz和156.25MHz时钟的时钟扩展

Vivado BFT内核可为测验不一起钟速率供给抱负设置,然后断定两个时钟是否为扩展时钟

为更好地了解Vivado规划套件核算未扩展时钟的办法,先以图1中的TCL脚原本对扩展恣意两个时钟速率之间的上升沿对上升沿途径要求的办法进行具体阐明。图2是这个脚本的输出,即两个别离运行在125MHz和156.25MHz的时钟的扩展。

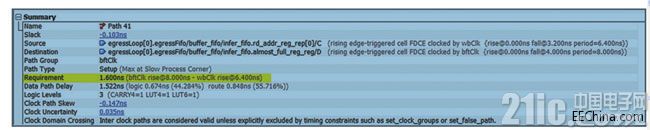

为承认上述TCL脚本得出的成果,咱们来调查一下Vivado BFT 内核典范规划。BFT 内核可为测验不一起钟速率供给抱负设置,然后断定两个时钟是否为扩展时钟。该内核有两个独立的时钟源,别离命名为wbClk和bftClk。时序束缚可将wbClk和bftClk的频率别离设置为100MHz和200MHz。用户可可对恣意两个时钟速率的此类束缚进行修正,以便承认由Vivado时序引擎判别的扩展联系。图3是将bftClk设置为125MHz,将wbClk设置为156.25MHz时所显现的成果,并供给了相关的时序(report_timing –from [get_clocks bftClk] -to [get_clocks wbClk])。请留意,由建议沿、捕获沿和时序要求一起承认TCL脚本的猜测成果。

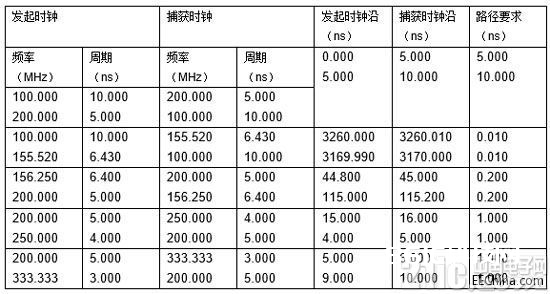

表1是运用图4中的TCL脚本取得的几种时钟速率的建议沿、捕获沿和途径要求。

图3:125MHz建议时钟到156.25MHz捕获时钟的时钟扩展

表1:时钟扩展实例

图4:时钟扩展Tcl 脚本

处理未扩展时钟

人们常常把未扩展时钟视为异步时钟,并经过FIFO、边缘检测器或同步器电路等恰当的同步技巧来进行处理。假如用户运用此类技巧,应在束缚中运用时序破例来处理未扩展时钟(一般运用set_false_path或set_max_delay破例)。

了解和阐明未扩展时钟具有重要的含义,由于时钟之间的边缘联系将决议Vivado规划套件中时序引擎所运用的途径要求。赛灵思期望对规划中的一切未扩展时钟进行详查,以保证运用恰当的同步技巧安全地穿越未扩展时钟之间的跨时钟域。