作者:邱陆陆

人工智能的风潮从技能一路蔓延到硬件,让“芯片”成为本年职业里盛极一时的主题。人们重视通用芯片范畴里CPU和GPU不断改写的基准(benchmark),更对专用芯片(ASIC)范畴不同场景下不断面世的解决计划表明出了空前的热心。

而众所周知,在专用芯片与通用芯片中心,还有一个更为灵敏,也更为奥秘的范畴:FPGA。无论是英特尔天价的收买仍是微软与 IBM 雄心壮志的计划,都让人对其愈加猎奇。而“全能芯片”的称号,以及多样化的责任规划:它可所以智能手机里不起眼的一个小组件,也可所以数千美金一块的开发板,也让人对其真面目愈加疑问。

FPGA 与深度学习的联系终究是什么?它合适加快何种类型的运算?合适运用于何种场景?6 月,机器之心采访了美国伊利诺伊大学香槟分校电气与核算机工程系(UIUC ECE)教授、深度学习算法硬件加快解决计划创业公司 Inspirit IoT 创始人陈德铭,与他聊了聊“全能芯片”FPGA 在深度学习范畴的用法。陈教授于近期宣告兼任国内核算机视觉范畴创业公司触景无限的首席科学家。

以下为采访实录。

机器之心:从算法的视点,FPGA 合适于加快哪些运算?

FPGA 的优势在于可定制化的并行。它可认为了特定算法专门定制逻辑单元。例如,算法中需求完结一个开三次方的运算,在通用芯片上需求一长串指令完结它,但是在 FPGA 上可认为这个特定运算规划一个单元。

定制化的一个“极限”的比方是,假如可以把神经网络中的参数悉数二值化、特征图(feature map)也悉数二值化,那么乃至可以不必乘法器,而是用异或门(XOR gate)完结核算,会有反常强壮的体现。即便不悉数二值化,由于悉数二值化会让准确度显着下降,只需合理运用各种低位宽的运算,仍可以让 FPGA 大放异彩。比方在咱们最近和 IBM 协作的 ELB-NN 项目中,咱们可以在功耗低于 5 瓦的景象下,让神经网络在 FPGA 上的算力到达 10.3 TOPS,一起仍然保持十分高的准确度。

另一个比方是微软的 Brainwave FPGA 项目,经过运用特别的 8-bit 的浮点运算,可以在高容量的 FPGA 上到达 40 TOPS。

值得一提的是,LSTM 等神经网络每一步操作都很类似,这种全体运算进程是序列的算法也十分适用于用 FPGA 进行加快。FPGA 十分拿手处理流数据,可以规划流水线机制,使得在运算进程中不需求将中心数据存入内存而是直接送到下一步进行操作。

机器之心:比较于其他芯片,FPGA 在完结深度学习模型时有哪些结构带来的优势?

FPGA 的引脚比一般的芯片多,一起它的逻辑单元可以彻底依据算法要求来重组然后发生定制化的数据通路(datapath),因而十分合适处理大批量流数据。它不像 GPU 相同需求重复调取片外存储中的数据,抱负状况时,只需数据一次性流进去再流出来,算法就完结了,因而,FPGA 十分合适具有低推迟需求的使命。

别的 FPGA 的速度快、功率低的特征也让它在能耗方面比较于 CPU、GPU 也有很大优势。

比方咱们在 FPGA 上完结了长时刻循环卷积网络(Long-term Recurrent ConvoluTIonal Network),它的速度 ( latency ) 比 GPU 快 3.1 倍,FPGA 的功率比 GPU 小 5.6 倍,终究全体能耗下降 17 倍左右。

机器之心:从职业的视点,FPGA 都可以用于哪些机器学习与深度学习使命的加快?

在终端,有些主动驾驶公司的车上体系中就选用了 FPGA 完结一些实时检测辨认使命。例如,我从前代表 UIUC 与小鹏轿车的副总裁、机器学习专家谷俊丽女士沟通,她说到,FPGA 可以凭仗信号处理和低能耗方面的优势,成为一个牢靠的第二体系,在轿车的榜首体系呈现失误的时分,作为安全形式介入进来。IoT 方面的运用就更多了,无论是安防仍是智能家居,FPGA 都会有时机进入商场。

在云端,也有结合 FPGA 的巨大空间。之前,微软的 Project Catapult 就建立起了大规划的 FPGA 云服务器。现在 Catapult 正在运转查找和数据存储方面的运算,一起,他们也在积极地考虑怎么把机器学习运算布置在上面,包含是否能将 FPGA 作为其 Azure 云的后端支撑。亚马逊 AWS 的 FPGA 云核算现已很有规划了,而且一直在大力推进之中。最近,国内创业公司深鉴也开端结合华为的云端 FPGA 来进行深度学习算法的加快,特别在依据 LSTM 的语音辨认上十分有优势。

机器之心:能否介绍一下运用高层次归纳(HLS)主动生成寄存器级(RTL)完结与手艺用硬件描绘言语(HDL)进行完结的差异?

关于深度学习相关算法来说,HLS 是有优势的。

当你阅览用高层言语描绘的深度学习模型时,你会发现模型是有规则的。比方,卷积操作在 C 言语里便是一个六层的嵌套循环。此刻我就可以针对这个循环开发一个 IP 核,确认怎么进行流水线规划(pipelining),怎么分配存储等,然后再将 IP 核用在 FPGA 上,然后让神经网络中的一切卷积层来同享 IP 核即可。

此刻规划的优化关键是 IP 核的巨细、是否需求多个 IP 核并行运算等。这是一个十分适用 HLS 的场景,由于 HLS 可以主动化地、快速地探究不同的解决计划。假如选用 RTL,则需求许多工程师,组成多个团队,每个团队依据工程师曩昔的规划经历侧重探究一个方向,这是一个本钱十分高的进程。

RTL 是一种描绘硬件的空间的联系和逻辑时序等逻辑联系的硬件描绘言语。这是一门难学的言语,可以熟练把握的从业者也不多,开发和测验都很慢。夸大点说,假如 HLS 开发周期以天和周来核算,那么 RTL 通常是以月和年。

从终究成果视点讲,RTL 彻底手艺调制的解决计划是很可能比 HLS 主动生成的计划作用好的。咱们从前做过比较,在深度学习的情境下,HLS 和 RTL 办法的距离在 10% 左右。

因而,问题在于是否乐意花 3-5 倍的时刻取得额定 10% 的作用。

机器之心:在简化 FPGA 开发进程这一使命上,研讨者做了哪些作业?

咱们的团队开发了一个研讨东西,是一个 C 言语的模板库,可以依据 Caffe 和 TensorFlow 的代码主动生成 C 言语的表达。然后研讨者可以将 C 言语的代码再交给 HLS 东西生成 RTL 代码。

C 言语是软件工程师遍及把握的言语,这样的东西让软件工程师也具有 FPGA 开发才能,而且让开发者更专心于算法,而不必过多考虑底层硬件。

而且,这个进程中的中心成果都可以导出,专业人员也可以在主动生成的根底上再进行优化,总而言之,整个开发的功率都得到了极大的进步。

这仅仅举一个比方。还有其它许多的研讨人员在做相关的进步深度学习规划功率和质量的各类东西和渠道。工业和学术届的都有。学术届比方 UCLA 的丛京生教师,以及 Cornell 的张志汝教师等。工业届比较抢先的是赛灵思和英特尔自己规划的一些东西。

机器之心:各个大公司在 FPGA 的运用方面都进行了哪些作业?拓宽商场的思路都有哪些?

IBM 和赛灵思正在 Power 系列上进行协作,致力于在 FPGA 上加更多的存储,在最新的原型机上,把存储加到了 64G,比较于市面上现在常见的最大 8 或 16G,极大扩展了数据带宽,来进行和大数据相关的处理。

英特尔收买了 Altera,而且致力于协助 Altera 进行编译等东西的开发。这是一个 FPGA 商品化的思路,就像 GPU 相同,说不定未来的 PC 里就会有一个 FPGA 协处理器在 CPU 周围完结作业。或许在芯片层面上,CPU 片上就有一块 FPGA。总而言之,一旦东西做好,整合的时时机有许多。英特尔在智能城市、才智制作方面都有许多的设想,而且期望借由 FPGA 完结。

再便是微软。它的思路首要便是云核算,除了 Bing 之外,也期望在进行机器学习使命的 Azure 云中运用 FPGA。

机器之心:能否介绍一下 Inspirit IoT 经过哪些产品完结了深度学习算法在 FPGA 上的加快?

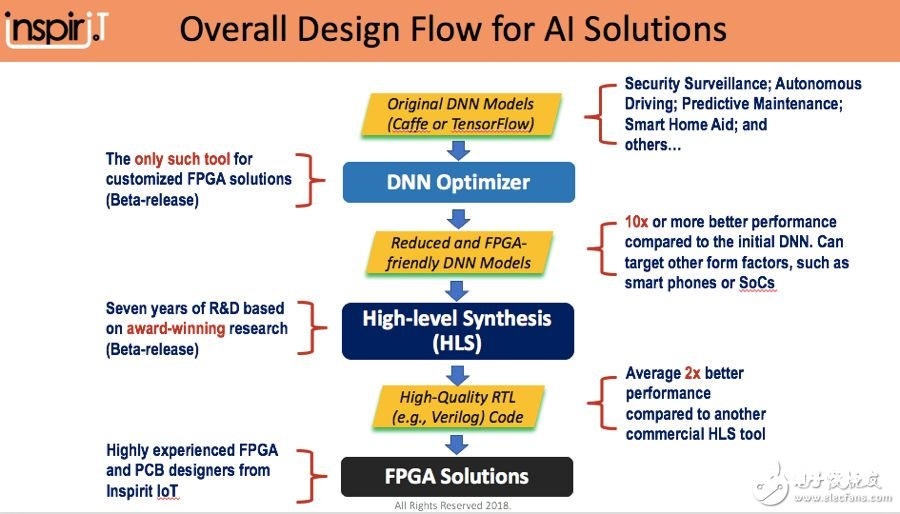

咱们公司首要有三个产品,依照层次分别是 DNN 优化器、高层次归纳加快编译器(HLS compiler),以及全体 FPGA 解决计划。

DNN 优化器的方针是定制一个 FPGA 友爱的模型,把练习好的模型中关于推理来说冗余的部分去掉。例如,练习时运用的浮点数可以被替换为定点数,练习时每层有十分多的单元,但是在推理的时分可以进行剪枝(Pruning),等等。DNN 优化器便是以各种高层结构的模型为根底,依据硬件的特性和场景的特性进行主动的优化。

高层次归纳编译器让开发者得以绕开写 Verilog 硬件描绘言语,将 C、 C++、CUDA 等代码直接编成 FPGA,旨在下降硬件开发的门槛,进步软件工程师的生产力。咱们的特征是这个编译器可以天然结合深度学习算法中的各种 IP 核,然后可以最好的优化各种深度学习算法在 FPGA 上的高速及高质量的完结。

除此之外,咱们也有嵌入 FPGA 的开发板,用于声响相关的运用场景。其上嵌入了 FPGA 和 4 个麦克风,可以检测声响来历、进步声响质量,也可以和摄像头号其他设备连用。例如,捕捉到车辆撞击声、尖叫声等特定声响之后,可以调转摄像头,录入相关的视频等,期望取得一个「1+1>3」的作用。