1. 运用布景

1.1 亚稳态发生原因

在FPGA体系中,假如数据传输中不满意触发器的Tsu和Th不满意,或许复位过程中复位信号的开释相关于有用时钟沿的恢复时刻(recovery time)不满意,就或许发生亚稳态,此刻触发器输出端Q在有用时钟沿之后比较长的一段时刻处于不确定的状况,在这段时刻里Q端在0和1之间处于振动状况,而不是等于数据输入端D的值。这段时刻称为决断时刻(resoluTIon TIme)。经过resoluTIon TIme之后Q端将安稳到0或1上,可是安稳到0或许1,是随机的,与输入没有必定的联系。

1.2 亚稳态发生场合

只需体系中有异步元件,亚稳态便是无法防止的,亚稳态首要发生在异步信号检测、跨时钟域信号传输以及复位电路等常用规划中。

1.3 亚稳态损害

因为发生亚稳态后,寄存器Q端输出在安稳下来之前或许是毛刺、振动、固定的某一电压值。在信号传输中发生亚稳态就会导致与其相连其他数字部件将其作出不同的判别,有的判别到“1”有的判别到“0”,有的也进入了亚稳态,数字部件就会逻辑紊乱。在复位电路中发生亚稳态或许会导致复位失利。怎样下降亚稳态发生的概率成了FPGA规划需求注重的一个注意事项。

2. 理论剖析

2.1 信号传输中的亚稳态

在同步体系中,输入信号总是体系时钟同步,能够抵达寄存器的时序要求,所以亚稳态不会发生。亚稳态问题一般发生在一些跨时钟域信号传输以及异步信号收集上。

它们发生的原因如下:

(1)在跨时钟域信号传输时,因为源寄存器时钟和意图寄存器时钟相移不知道,所以源寄存器数据宣布数据,数据或许在任何时刻抵达异步时钟域的意图寄存器,所以无法确保满意意图寄存器Tsu和Th的要求;

(2)在异步信号收会集,因为异步信号能够在恣意时刻点抵达意图寄存器,所以也无法确保满意意图寄存器Tsu和Th的要求;

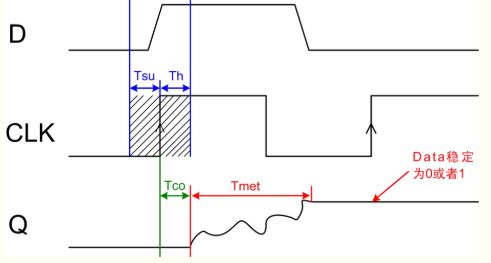

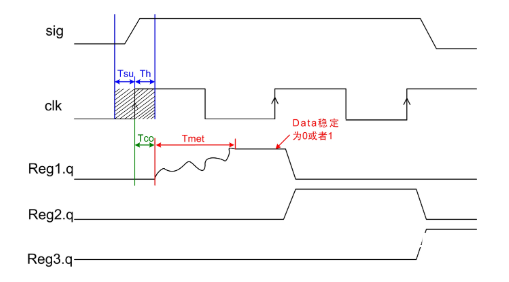

当数据在意图寄存器Tsu-Th时刻窗口发生改变,也即当数据的树立时刻或许坚持时刻不满意时,就或许发生亚稳态现象。如图3.1所示。

图3.1 亚稳态发生示意图

由图可知,当发生亚稳态后Tco时刻后会有Tmet(决断时刻)的振动时刻段,当振动完毕回到安稳状况时为“0”或许“1”,这个是随机的。因而,会对后续电路判别形成影响。

2.2 复位电路的亚稳态

2.2.1 异步复位电路

在复位电路规划中,复位信号根本都是异步的,常用异步复位电路Verilog描绘如下:

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) a <= 1’b0;

else a <= b;

end

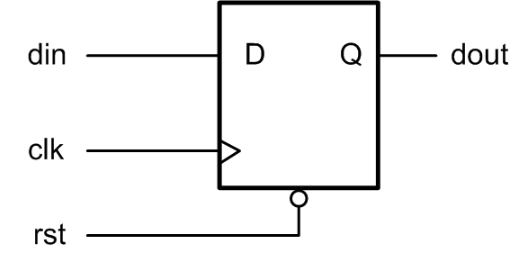

归纳出来复位电路模型如图3.2所示:

图3.2 异步复位电路模型

如图3.3所示,为复位电路复位时序图。假如异步复位信号的吊销时刻在Trecovery(恢复时刻)和Tremoval(移除时刻)之内,那必然形成亚稳态的发生,输出在时钟边缘的Tco后会发生振动,振动时刻为Tmet(决断时刻),终究安稳到“0”或许“1”,就会或许形成复位失利。

图3.3 异步复位时序

2.2.2 同步复位电路的亚稳态

在复位电路中,因为复位信号是异步的,因而,有些规划选用同步复位电路进行复位,并且绝大多数材料关于同步复位电路都以为不会发生亚稳态,其实不然,同步电路也会发生亚稳态,仅仅几率小于异步复位电路。

如下面verilog代码对同步复位电路的描绘。

always @(posedge clk)

begin

if(!rst_n) a <= 1’b0;

else a <= b;

end

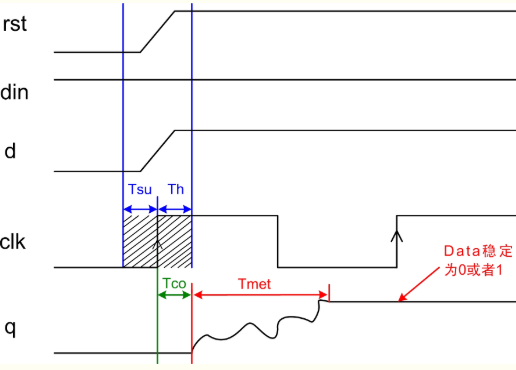

归纳出硬件电路如图3.4所示。

图3.4 同步复位电路

在此,咱们不评论同步复位的耗费资源问题,只评论同步复位的亚稳态发生状况。

当输入端Din为高电平,并且复位信号的吊销时刻在clk的Tsu和Th内时分,亚稳态就随之发生了。如图3.5时序所示,当复位吊销时刻在clk的Tsu和Th内,输入数据为“1”,经过和输入数据相与后的数据也在clk的Tsu和Th内,因而,必然会形成相似异步信号收集的亚稳态状况。

图3.5 同步复位电路时序图

2.3 亚稳态发生概率以及串扰概率

在实践的FPGA电路规划中,常常人们想的是怎样削减亚稳态对体系的影响,很少有人考虑怎样才干削减亚稳态发生几率,以及亚稳态串扰的概率问题。

2.3.1 亚稳态发生概率

由上面剖析得知,体系亚稳态发生的都是因为clk的Tsu和Th不满意,又或许是复位信号的移除和恢复时刻不满意。常用FPGA器材的Tsu+Th约等于1ns,复位移除和恢复时刻相加约等于1ns。

当异步信号不是一组数据,或许信号量较少,那就需求对异步信号进行同步处理,例如对一个异步脉冲信号进行收集,只需脉冲信号改变发生在时钟Tsu和Th窗口内,那就很或许会发生亚稳态,亚稳态发生的概率大约为:

概率 = (树立时刻 + 坚持时刻)/ 收集时钟周期 (公式3-1)

由公式3-1能够看出,跟着clk频率的添加,亚稳态发生的几率是添加的。

例如,为体系选用100M时钟对一个外部信号进行收集,收集时钟周期为10ns,那收集发生亚稳态的概率为:1ns/10ns = 10%

同理选用300M时钟对一个外部信号进行收集,那发生亚稳态的概率为:1ns/3.3ns = 30%

假如选用三相相位差为120°的时钟对一个外部信号进行收集,那发生亚稳态的概率挨近90%

所以在异步信号收集过程中,要想削减亚稳态发生的概率:

(1) 下降体系作业时钟,增大体系周期,亚稳态概率就会减小;

(2) 选用工艺更好的FPGA,也便是Tsu和Th时刻较小的FPGA器材;

2.3.2 亚稳态的串扰概率

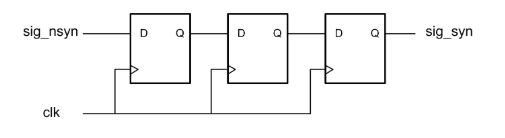

运用异步信号进行运用的时分,好的规划都会对异步信号进行同步处理,同步一般选用多级D触发器级联处理,如图3.6所示,选用三级D触发器对异步信号进行同步处理。

图3.6 三级寄存器同步

这种模型大部分材料都说的是榜首级寄存器发生亚稳态后,第二级寄存器安稳输出概率为90%,第三极寄存器安稳输出的概率为99%,假如亚稳态跟从电路一向传递下去,那就会另自我修护才能较弱的体系直接溃散。接下来咱们剖析这种串扰的概率问题。

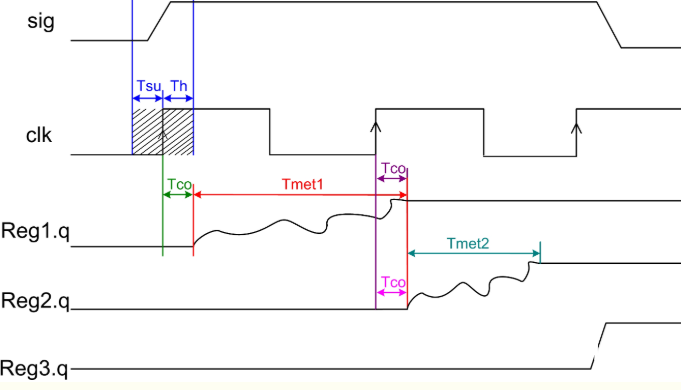

如图3.7所示为一个正常榜首级寄存器发生了亚稳态,第二级、第三极寄存器消除亚稳态时序模型。

图3.7 三级寄存器消除亚稳态

由上图能够看出,当榜首个寄存器发生亚稳态后,经过Tmet的振动安稳后,第二级寄存器能收集到一个安稳的值。可是为什么第二级寄存器仍是或许会发生亚稳态呢?

因为振动时刻Tmet是遭到许多要素影响的,所以Tmet时刻又长有短,所以当Tmet时刻长到大于一个收集周期后,那第二级寄存器就会收集到亚稳态。如图3.8所示。

图3.8 二级寄存器亚稳态

由上图可知,第二级也是一个亚稳态,所以在这种状况下,亚稳态发生了串扰,从榜首级寄存器传到了第二级寄存器,相同也或许从第二级寄存器串扰到第三级寄存器。这样会让规划逻辑判别犯错,发生亚稳态传输,或许导致体系死机奔溃。

2.3.3 亚稳态振动时刻Tmet

亚稳态震动时刻Tmet联系到后级寄存器的收集安稳问题,Tmet影响要素包含:器材的生产工艺、温度、环境以及寄存器收集到亚稳态离安稳态的时刻等。乃至某些特定条件,如搅扰、辐射等都会形成Tmet增加。

3. 运用剖析

有亚稳态发生,咱们就要对亚稳态进行消除,常用对亚稳态消除有三种方法:

(1) 对异步信号进行同步处理;

(2) 选用FIFO对跨时钟域数据通讯进行缓冲规划;

(3) 对复位电路选用异步复位、同步开释方法处理。

3.1.1 对异步信号进行同步提取边缘

在异步通讯或许跨时钟域通讯过程中,最常用的便是对异步信号进行同步提取边缘处理。对一个异步信号进行提取上升沿一般选用程序清单 4.1所示。

程序清单 4.1 双极寄存器提取边缘

input sig_nsyn;

wire sig_nsyn_p;

reg[1:0] sig_nsyn_r;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) sig_nsyn_r <= 2’d0;

else sig_nsyn_r <= { sig_nsyn_r [0], sig_nsyn };

end

assign sig_nsyn_p = sig_nsyn_r[0] & ~sig_nsyn_r[1];

这种边缘提取方法关于一个安稳的体系是不合适的,例如:当榜首级寄存器收集到亚稳态,那必然形成sig_nsyn_p输出亚稳态,这样就会对选用sig_nsyn_p的信号进行判别的电路形成影响,乃至判别犯过错的值。

依据3.3.1末节的亚稳态发生概率,假如在100M时种下那榜首级寄存器发生亚稳态的概率约为10%,跟着体系收集频率升高,那发生亚稳态的概率也会随之上升。因而,在进行异步信号跨频提取边缘时分,一般选用多进行一级寄存器消除亚稳态,或许在体系安稳性要求高的状况下,选用更多级寄存器来消除亚稳态,如程序清单 4.2所示,即为选用4级寄存器消除亚稳态,相应的边缘信号发生的时刻就晚了两个时钟周期。

程序清单 4.2 多级寄存器提取边缘信号

input sig_nsyn;

wire sig_nsyn_p;

reg[3:0] sig_nsyn_r;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) sig_nsyn_r <= 2’d0;

else sig_nsyn_r <= { sig_nsyn_r [2::0], sig_nsyn };

end

assign sig_nsyn_p = sig_nsyn_r[2] & ~sig_nsyn_r[3];

3.1.2 FIFO进行异步跨频数据处理

当数据流从一个时钟域到另一个时钟域的时分,绝大多数状况下都选用FIFO来作为中心缓冲,选用双时钟对数据缓冲,就能够防止亚稳态的发生。

3.1.3 异步复位,同步开释

关于复位状况下的亚稳态,常常是因为恢复时刻和移除时钟不满意形成的,因而,最常用的处理方法是选用异步复位、同步开释。常用电路模型如所示。选用第二级寄存器输出作为大局复位信号输出。

程序清单 4.3 异步复位处理

wire sys_rst_n;

reg [1:0] rst_r;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) rst_r <= 2’d0;

else rst_r <= {rst_r[0], 1’b1};

end

assign sys_rst_n = rst_r[1];

经过上面三种方法处理异步信号、异步数据、以及异步复位可有用的进步体系的安稳性。削减亚稳态的发生。