依据FPGA根本数据流的下载操控方法,运用遗传算法,经过单片机操控数据流的方法对FPGA进行编程装备,完结本身重构,使体系具有自习惯、自组织和自修正的特性。

本文完结了依据遗传算法的硬件演化进程。经过Mcu随机发生种群,挑选好的基因进行穿插变异发生子孙,然后将适宜的基因经过测验找到最佳重构计划。挑选最佳计划应用于硬件,完结自我修正和自习惯。

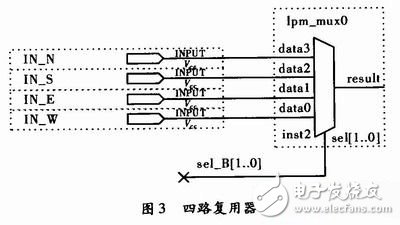

1 软件算法

遗传算法(GeneTIc Algorithm,GA)是由美国密执安大学John Holland教授于20世纪70年代提出并逐步开展起来的一种自习惯大局优化搜索算法。他模仿天然挑选和天然遗传进程发生的繁衍,穿插和基因突变现象,在每次迭代中都保存一组候选解,并按某种方针从群解中选取较优个别,运用遗传算子对这些个别进行组合,发生新一代的候选解群,直到满意某种收敛方针,终究得到问题的最优解或近似解。

根本遗传算法由4部分组成:(1)编码(发生初始种群)。(2)习惯度函数核算。(3)遗传算子(挑选、穿插、变异)。(4)运转参数。

1.1 挑选

遗传算法首先要发生初始种群,一般叫做染色体。染色体由基因组成,如11001,每位二进制数便是一个基因变量,然后经过习惯度函数检测合格的染色体,挑选合格染色体进行下一步的穿插、变异,得到新个别。

遗传算法中的习惯度,是表明某一个别对环境的习惯才能,也表明该个别繁衍子孙的才能。遗传算法的习惯度函数也叫点评函数,是用以判别集体中个别好坏程度的方针,它是依据所求问题的方针函数进行评价的。

此处习惯度挑选函数的形式经过一种反应形式,将发生的个别经过仿真检测评价。假如到达要求,经评价成果存入存储模块,然后以轮盘赌的方法对一切的函数成果加权,判别每个基因的习惯度与加权和的比值,即介于(0,1)的小数,挑选大于—个值比方0.8为合格,当评价完集体中一切个别的习惯度后,挑选习惯度大于0.8的个别存储,然后等候由穿插变异模块发生出的新个别。

1.2 穿插变异

穿插变异模块得到来自挑选模块的两个个别,依据随机数模块发生的随机数与穿插概率作比较,判别是否进行穿插操作。穿插算子依据穿插率将种群中的两个个别随机交流某些基因,能够发生新的基因组合,希望将有利基因组合在一起。

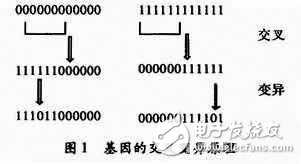

如找到两个父代基因,需求进行穿插,找到基因的穿插点,将各个基因的穿插点穿插基因变量构成新的基因变量,变异便是每个基因找到基因变异点,企图经过基因变异找到适宜的计划,如图1所示。

1.3 基因下载

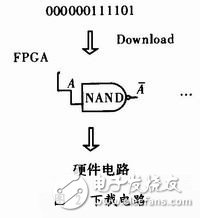

得到的优秀基因便是所需的计划,将这个计划直接下载,最终完结可操控,可重构,自习惯。如图2所示。

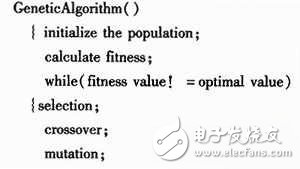

根本遗传算法是经过某种编码机制把目标笼统为由特定符号按必定次序排成的串,就像染色体都是由基因排成的串,此处是运用二进制编码,得到的是5 bit二进制字符串。程序如下:

2 FPGA根本结构

现在干流FPGA均选用依据SRAM工艺的查找表结构,也有些军品和宇航级FPGA,选用Flash或熔丝与反熔丝工艺的查找表结构。经过烧写文件改动查找表内容的方法来完结对FPGA的重复装备。

查找表(Look-Up-Table)简称为LUT,现在FPGA中多运用4输入的LUT,所以每个LUT能够当作一个有4位地址线的RAM。这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出。

2.1 多路复用器(MulTIplexer)

依据这种4输入LUT结构的原理,选用了4输入的复用挑选器,在多路数据传送进程中,能够依据需求将其间恣意一路选出,也称多路挑选器或多路开关。本文将操控器发生的5位数据流经过移位寄存器来操控4个输入端口的挑选,如图3所示。

2.2 移位寄存器(Shift Register)

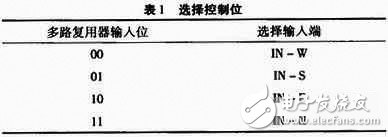

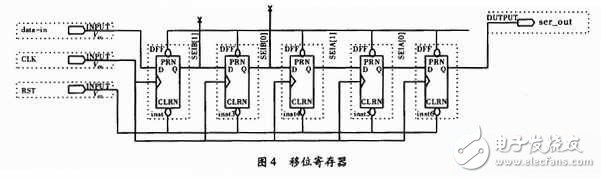

在数字电路中,一般会用寄存器寄存二进制数据或代码,如图4所示。Mux的挑选位由操控器发生的数据流经缓存后输出,SelA[1,0],SelB[1,O]别离作用于两个多路复用器。移位寄存器中输出操控多路复用器的操控位如表1所示。

2.3 与非门

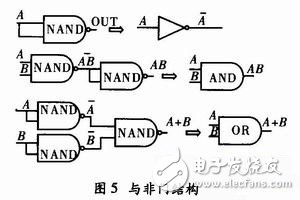

与非门是组成各种电路的根底门,可依据需求,用与非门建立不同的门,如图5所示,将不同的与非门结构完结与门或门等其他功用,完结动态可重构。

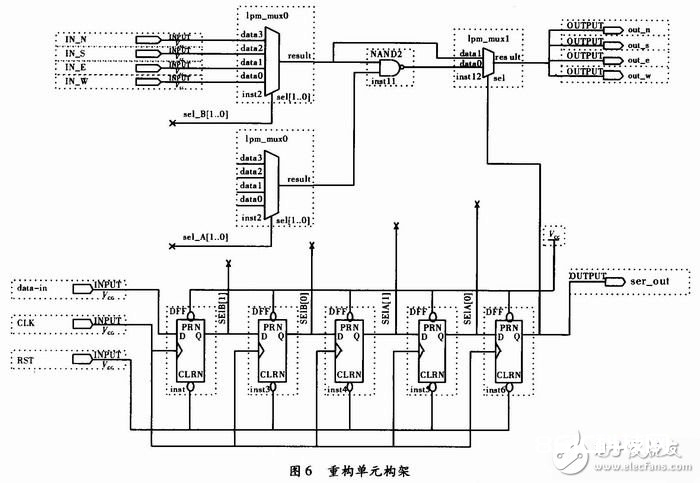

3 可重构体系的单元结构建立

依据4输入LUT的结构原理,本电路选用2个4输入的MUX用来挑选与非门的输入端口,然后用1个2输入的MUX挑选数据的输出,3个MUX的挑选位别离用SelB[1,0],SelA[1,0],Sel-out操控,移位寄存器作为5位串行二进制数的缓存,如图6所示。可知,与非门能够经过东西南北4输入的挑选组成各种数字电路,这种单元结构能够持续扩展为2&TImes;2或更多单元,完结杂乱的数字电路。这儿演示单元结构构成的与门和或门的简略结构,进一步阐明可重构的可完结性。

当发生数据流经过缓存进行重构电路后,能够看到新的了解电路所完结的功用,如图7所示。经过调查输入和输出端的联系,测验得到所需电路的最佳计划,即可下载到硬件,完结所需使命。

4 硬件渠道结构

硬件结构是依据单片机与FPGA的通讯。Mcu挑选MSP430,经过RS232和FPGA进行通讯,PC机经过JTAG接口向中心芯片下载程序。外围设备中,挑选2个8位LED,4位输入按键,1个12864液晶显示,预留32位的扩展接口。如图8所示,FPGA挑选的是Ahera的EP1C16Q240C8。

5 小结

施行电路可重构技能,已成为核算体系研究中的新热门,使硬件逐步软件化,经过微处理器结合多个FPGA对其进行装备,完结动态部分可重构,具有较强的通用性和自习惯性,适用于模块化规划。本文依据5 bit数据流,完结了FPGA的部分动态可重构,能够实时生成所需求的硬件结构。动态可重构能够充分运用可重装备硬件,尤其是可重装备核算方面。该技能有理论上有较大开展,FPGA未来的开展方向之一便是做支撑动态可装备的SOPC硬件。