AD4022相关信息来自ADI官网,详细参数以官网发布为准,AD4022供给信息可在查IC网查找相关供给商。

产品概况

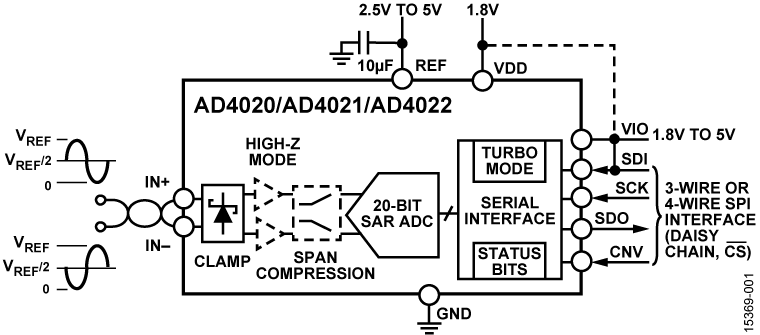

The AD4022 is a high accuracy, high speed, low power, 20-bit, Easy Drive, precision successive approximation register (SAR) analog-to-digital converter (ADC) that operates from a single power supply, VDD. The reference voltage, VREF, is applied externally and can be set independent of the supply voltage. The AD4022 power scales linearly with throughput.

Easy Drive features reduce both signal chain complexity and power consumption while enabling higher channel density. The reduced input current, particularly in high-Z mode, coupled with a long signal acquisition phase, eliminates the need for a dedicated ADC driver. Easy Drive broadens the range of companion circuitry that is capable of driving these ADCs (see Figure 2).

Input span compression eliminates the need to provide a negative supply to the ADC driver amplifier while preserving access to the full ADC code range. The input overvoltage clamp protects the ADC inputs against overvoltage events, minimizing disturbances on the reference pin, and eliminating the need for external protection diodes.

Fast device throughput up to 500 kSPS allows users to accurately capture high frequency signals and to implement oversampling techniques to alleviate the challenges associated with antialias filter designs. Decreased serial peripheral interface (SPI) clock rate requirements reduce digital input/output power consumption, broadens digital host options, and simplifies the task of sending data across digital isolation. The SPI-compatible serial user interface is compatible with 1.8 V, 2.5 V, 3 V, and 5 V logic by using the separate VIO logic supply.

Applications

- Automatic test equipment

- Machine automation

- Medical equipment

- Battery-powered equipment

- Precision data acquisition systems

- Instrumentation and control systems

优势和特色

- Easy Drive

- Greatly reduced input kickback

- Input current reduced to 0.5 μA/MSPS

- Enhanced acquisition phase, ≥88% of cycle time at 500 kSPS

- First conversion accurate, no latency or pipeline delay

- Input span compression for single-supply operation

- Fast conversion allows low SPI clock rates

- Input overvoltage clamp protection sinks up to 50 mA

- SPI-/QSPI-/MICROWIRE-/DSP-compatible serial interface

- Greatly reduced input kickback

- High performance

- Differential analog input range: ±VREF, VREF from 2.4 V to 5.1 V

- Throughput: 500 kSPS options

- INL: ±3.1 ppm maximum

- Guaranteed 20-bit no missing codes

- SNR: 100.5 dB at fIN = 1 kHz at VREF = 5 V

- THD: −123 dB at fIN = 1 kHz, −100 dB at fIN = 100 kHz

- SINAD: 92 dB at fIN = 250 kHz (see Figure 17)

AD4022电路图

AD4022中文PDF下载地址

AD4022下载链接地址:https://www.analog.com/media/en/technical-documentation/data-sheets/AD4020-4021-4022.pdf