ADSP-SC571相关信息来自ADI官网,详细参数以官网发布为准,ADSP-SC571供给信息可在查IC网查找相关供给商。

产品概况

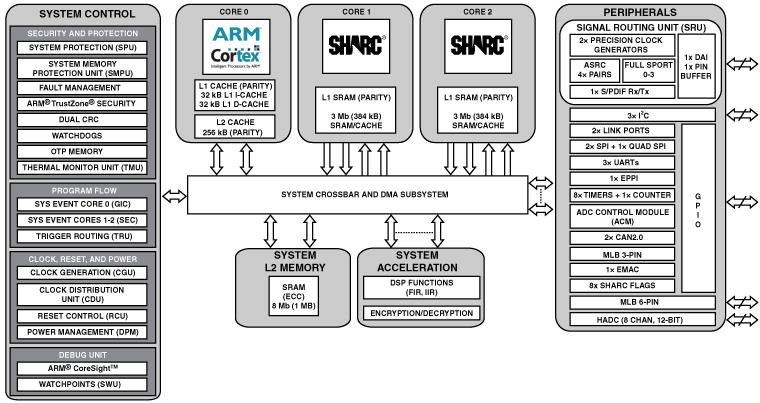

ADSP-SC57x/ADSP-2157x处理器归于SHARC®系列产品。ADSP-SC57x处理器根据SHARC+®双核和ARM®Cortex®-A5内核。ADSP-SC57x/ADSP-2157x SHARC处理器归于单指令多数据(SIMD) SHARC系列数字信号处理器(DSP),选用ADI公司的Super Harvard架构。这些32/40/64位浮点处理器针对高性能音频/浮点使用进行了优化,具有大容量片内静态随机存取存储器(SRAM),可消除输入/输出(I/O)瓶颈的多条内部总线,而且供给立异的数字音频接口(DAI)。SHARC+内核最新参加的特性包含缓存增强和分支猜测,一起坚持指令集兼容之前的SHARC产品。

ARM Cortex-A5和SHARC处理器集成了一组业界抢先的体系外设和存储器,在一个集成封装中供给精简指令集计算机(RISC)式编程才能、多媒体支撑和先进的信号处理,可谓相似使用的首选渠道。这些使用包含很多商场范畴,包含轿车、专业音频和需求高性能浮点处理的工业使用。

优势和特色

- 两个增强型SHARC+高性能浮点内核

- 每个SHARC+内核最高达500 MHz

- 每个内核最多有3 Mb (384 kB) L1 SRAM存储器,支撑奇偶校验,可装备为缓存(可选功用)

- 支撑32位、40位和64位浮点

- 32位定点

- 字节、短字、字、长字寻址

- ARM Cortex-A5内核

- 500 MHz/800 DMIPS,支撑NEON/VFPv4-D16/Jazelle

- 支撑奇偶校验的32 kB L1指令缓存/支撑奇偶校验的32 kB L1数据缓存

- 支撑奇偶校验的256 kB L2缓存

- 强壮的DMA体系

- 片内存储器维护

- 集成安全特性

- 17 mm × 17 mm 400引脚CSP_BGA和176引脚LQFP_EP封装,契合RoHS规范

- 在轿车使用温度范围内的体系功耗低

存储器

- 最多1 MB的大容量片内L2 SRAM,具有ECC维护功用

- 一个针对低体系功耗而优化的L3接口,供给与DDR3(支撑1.5 V DDR3L器材)、DDR2或LPDDR1 SDRAM器材相连的16位接口

其他特性

- 安全和维护

- 加密硬件加快器

- 快速安全引导,支撑IP维护

- 支撑ARM TrustZone

- 加快器

- FIR、IIR加快引擎

- 经过轿车使用认证

ADSP-SC571电路图

ADSP-SC571中文PDF下载地址

ADSP-SC571下载链接地址:https://www.analog.com/media/cn/technical-documentation/data-sheets/ADSP-SC570_571_572_573_ADSP-21571_573_cn.pdf