(文章来历:润石科技)

模仿开关,是运用JFET或MOS的特性完结操控信号通路的开关,首要用来完结信号链路衔接或断开的切换功用。因为它具有功耗低、速度快、无机械触点、体积小和运用寿命长等特色,在各种自动操控系统和电子数码产品中得到了广泛使用。

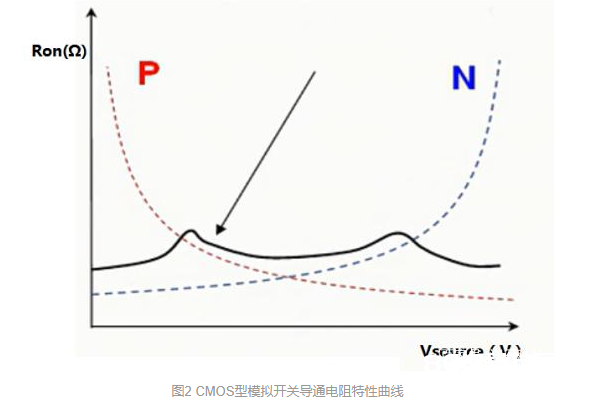

传统CMOS工艺模仿开关的结构如图1所示。将NMOS与PMOS并联,可使信号在两个方向上平等顺利地经过。门极用于操控开关的导通和截止,NMOS在Vgs为正的时分导通,在Vgs为负的时侯截止,PMOS则反之。因为PMOS和NMOS的不同特性,导致他们组成的开关具有如下图所示的特性。NMOS和PMOS之间承载信号电流的多少由输入与输出电压比决议。因为开关对电流流向不存在挑选问题,因此也没有输入端与输出端之分。两个MOSFET由内部反相与同相逻辑操控下导通或断开。CMOS开关的优点是轨到轨的动态规模,双向操作,在输入电压变化时,导通电阻坚持不变。

静态参数(导通电阻,漏电流,逻辑操控触发电平):①导通电阻RON,不同通道导通电阻的差异RON,导通电阻的平整度RFLAT(ON)。

导通电阻会导致信号有丢失,尤其是当开关串联的负载为低阻抗时丢失更大。使用中应根据实际情况挑选导通电阻适宜的开关。特别需求留意,导通电阻的阻值与电源供电电压有直接关系,一般电源电压越大,导通电阻就越小。

NMOS管在信号比较低时的导通电阻较小,而PMOS管则在输入信号较高时的导通电阻较小,两个电阻并联后,则在整个信号的有用规模内都比较低。

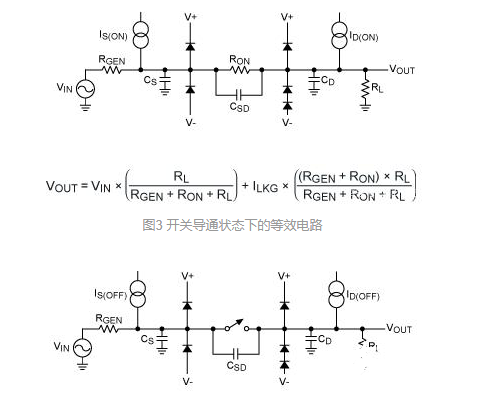

漏电流Leakage Current :一个抱负状况的开关要求导通状况下的电阻为零,断开状况下导通电阻趋于无限大,漏电流为零;而实际上开关断开时为高阻状况,漏电流不为零,惯例的CMOS漏电流约1nA左右。开关断开时,漏电流会流入负载,然后引起额定的差错。假如信号源内阻很高,传输信号为直流量,就特别需求考虑模仿开关的漏电流,一般期望漏电流越小越好。

需求留意,假如经过模仿开关前端电路的阻抗大则漏电流的影响不容疏忽,假如前端电路阻抗较小,则导通电阻的影响就会更大些。

逻辑操控触发电平VIH,VIL。VIH能够被模仿开关识别成逻辑高电平的最小电平值;VIL能够被模仿开关识别成逻辑低电平的最大电压值。

(责任编辑:fqj)