边缘D触发器

触发器是一种时钟操控的回忆元件,触发器具有一个操控输入信号(CLOCK),CLOCK信号是触发器只在特定时间才按输入信号改动输出状况。若触发器只在时钟由L到H(H到L)的转化时间承受输入,则称这种触发器是上升沿(下降沿)触发的。

边缘D触发器也称为坚持-堵塞边缘D触发器。负跳沿触发的主从触发器作业时,必须在正跳沿前参加输入信号。假如在CP 高电平期间输入端呈现搅扰信号,那么就有可能使触发器的状况犯错。而边缘触发器答应在CP触发沿来到前一会儿参加输入信号。这样,输入端受搅扰的时间大大缩短,受搅扰的可能性就降低了。

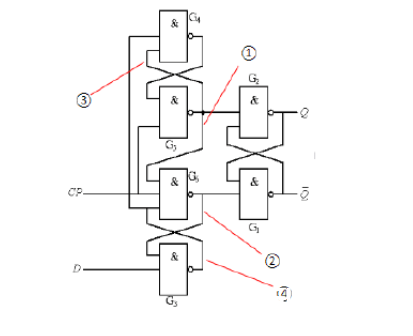

①为堵塞复位线,②为坚持复位线,③为坚持置位线,④为堵塞置位线。触发器输出为1时,使用坚持置位线和堵塞复位线,坚持输出不变。触发器输出为0时,使用坚持置位线和堵塞复位线,坚持输出为复位状况。

边缘触发器的类型许多,有使用CMOS传输门的边缘触发器、坚持堵塞型触发器,有使用门电路传输推迟时间的边缘触发器等。不管哪种类型的边缘型触发器,都能完结触发器的次态只是取决于CP时钟脉冲的下降沿(或上升沿)抵达时间输入信号的状况,而与其他时间触发器输入信号的状况无关。因而,边缘型触发器大大提高了作业的可靠性,增强了抗搅扰才干。下面使用门电路传输推迟时间的边缘触发器为例,介绍边缘触发器的作业原理。

作业原理

1)CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状况不变。一起,因为Q3至Q5和Q4至Q6的反应信号将这两个门翻开,因而可接纳输入信号D,Q5=D,Q6=Q5=D。 2)当CP由0变1时触发器翻转。这时G3和G4翻开,它们的输入Q3和Q4的状况由G5和G6的输出状况决议。Q3=Q5=D,Q4=Q6=D。由根本RS触发器的逻辑功用可知,Q=D。 3)触发器翻转后,在CP=1时输入信号被封闭。这是因为G3和G4翻开后,它们的输出Q3和Q4的状况是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反应线将G5封闭,即封闭了D通往根本RS 触发器的途径;该反应线起到了使触发器坚持在0状况和阻挠触发器变为1状况的效果,故该反应线称为置0坚持线,置1堵塞线。Q4为0时,将G3和G6封闭,D端通往根本RS触发器的途径也被封闭。Q4输出端至G6反应线起到使触发器坚持在1状况的效果,称作置1坚持线;Q4输出至G3输入的反应线起到阻挠触发器置0的效果,称为置0堵塞线。因而,该触发器常称为坚持-堵塞触发器。总归,该触发器是在CP正跳沿前承受输入信号,正跳沿时触发翻转,正跳沿后输入即被封闭,三步都是在正跳沿后完结,所以有边缘触发器之称。与主从触发器比较,同工艺的边缘触发器有更强的抗搅扰才干和更高的作业速度。

1、电路结构和作业原理

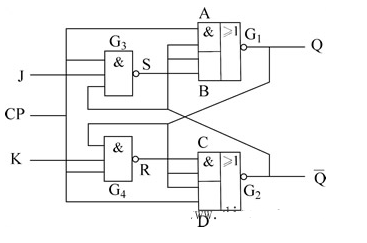

图1所示为使用门电路传输推迟时间的边缘JK触发器。

图1 边缘JK触发器

由图1可知,该电路由两个与或非门G1、 G2和两个与非门G3、G4组成。其间G1、 G2组成根本RS触发器,G3、G4组成输入操控电路。G3、G4门的传输推迟时间大于根本RS触发器的翻转时间。

当CP=0时,G3、G4门被锁定在高电平,输入信号J、K被封闭,即R=S=1。一起与门A、C被封闭,根本RS触发器通过与门B、D传输。此刻因为R=S=1,因而根本RS触发器状况坚持不变。即CP=0时,不管输入端J、K状况怎么,触发器坚持原态不变。

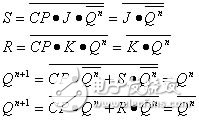

当CP=1时,G3、G4、A、C门均被翻开,此刻各门电路的输出为

(1)

(1)

可见,当CP=1时,不管输入端J、K状况怎么,触发器坚持原态不变。

当CP的上升沿抵达时(CP从0跳转为1的瞬间),门A、C首要被翻开,因为G3、G4、传输推迟的存在,输入端J、K的改变不影响G3、G4的输出,S、R仍为1,此刻触发器状况依然坚持原态。当推迟往后,触发器依然坚持原态不变,剖析进程同CP=1时。因而,当CP为上升沿时触发器坚持原态不变。

当CP的下降沿抵达时(CP从1跳转为0的瞬间),因为CP直接加在G1、G2和门外侧的两个与门A、C上,门A、C首要被封闭,其外侧的两个与门B、D的输入端S、R则需求通过一个传输推迟时间才干随CP=0而变为1。因而,在S、R没有变为“1”之前,依然坚持CP下降前的值,即

设CP的下降沿抵达前,触发器的状况为Qn=0, =1,输入端J=1,K=0,此刻G3、G4的输出为S=0,R=1。当CP的下降沿抵达的瞬间,G1门的两个与门A、B各有一个输入为零,故此刻G1门的输出Qn+1=1。G1门的输出反应到G2的两个输入上,与门C的两个输入均为“1”,使G2门的输出

=1,输入端J=1,K=0,此刻G3、G4的输出为S=0,R=1。当CP的下降沿抵达的瞬间,G1门的两个与门A、B各有一个输入为零,故此刻G1门的输出Qn+1=1。G1门的输出反应到G2的两个输入上,与门C的两个输入均为“1”,使G2门的输出 。G2门的输出

。G2门的输出 又反应到G1门的输入端。因为G3门的传输推迟时间满足长,能够确保在S消失低电平之前,

又反应到G1门的输入端。因为G3门的传输推迟时间满足长,能够确保在S消失低电平之前, 的低电平现已反应到了B门的输入端,使G1门的输出依然坚持高电平。当G3、G4门推迟之后,G3、G4被封闭,输入端J、K的改变不再影响输出,其输出S=R=1,因而根本RS触发器坚持原态不变。

的低电平现已反应到了B门的输入端,使G1门的输出依然坚持高电平。当G3、G4门推迟之后,G3、G4被封闭,输入端J、K的改变不再影响输出,其输出S=R=1,因而根本RS触发器坚持原态不变。

当输入端J、K取其他状况的值时,其剖析办法相同,请读者自行剖析。

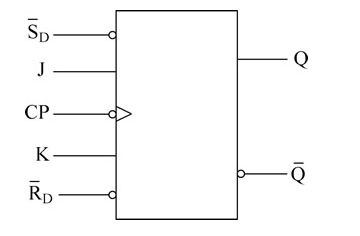

使用上述剖析办法,能够得到图6-2-8 所示边缘型JK触发器的特性表如表1所示。其逻辑图形符号如图2所示。

图2 边缘JK触发器的图形符号

依据触发时间的不同,边缘型触发器又分为上升沿和下降沿触发器两种类型。假如触发器是在时钟脉冲CP的下降沿触发,即为下降沿边缘触发器,逻辑符号中时钟脉冲CP靠边框处的圆圈表明下降沿触发,符号“》”表明边缘触发类型。假如触发器是在时钟脉冲CP的上升沿触发,即为上升沿边缘触发器,逻辑符号中时钟脉冲CP靠边框处没有圆圈表明上升沿触发。

2、动作特色

从上面的剖析可知,边缘触发器的次态只是取决于时钟脉冲CP的下降沿(或上升沿)抵达时输入端的逻辑状况,而与其他时间输入端的状况无关。这便是边缘触发器的动作特色。这一特色大大提高了触发器的作业稳定性和抗搅扰才干,在数字电路中得到广泛的使用。

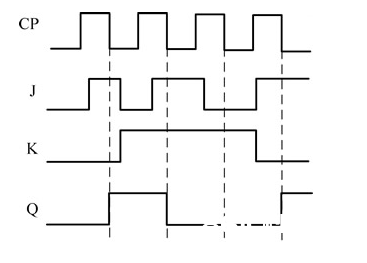

例1 在图3所示的下降沿边缘JK触发器电路中,已知时钟脉冲CP的波形和触发器输入端J、K的波形如图3所示。试画出触发器输出端Q的波形。设触发器的初始状况为0。

图3 例1图