Lluis Beltran Gil (ADI公司 精细转化器部SAR ADC运用团队,西班牙 瓦伦西亚)

摘 要:介绍了依据SAR ADC的体系和依据sigma-delta (∑-Δ) ADC的散布式数据搜集体系同步的传统办法、探讨了这两种架构之间的差异,并评论了同步多个Σ-Δ ADC时遇到的典型不方便。最终,提出一种依据AD7770采样速率转化器(SRC)的立异同步办法,该办法显现如安在不中止数据流的状况下,在依据Σ-ΔADC的体系上完结同步。

要害词:sigma-delta:ADC;散布式;数据搜集

0 导言

您是否从前幻想过,自己正坐在一辆打破音障的超音速飞机上?自从协和式超音速喷气客机退役后,这好像现已成了一个不或许完结的愿望,除非您是一名军机驾驶员或是宇航员。

身为一名电子工程师,笔者对全部事物的运作办法十分入神,比如对布谷鸟钟,我很猎奇它的每个独立体系怎么与其他体系调和地坚持同步。

咱们日子的各方面也是这样。咱们日子在一个彼此联络的国际,全部都是同步的——从银行服务器到智能手机的警报。差异在于各种特定状况下要处理的问题的巨细或杂乱性、不同体系的同步与所需的精度(或许容差),或许要同步的体系的巨细。

1 散布式体系

在独立规划中,运用的本地时钟或振荡器本身就会进行同步。可是,当独立规划需求集成到更广泛的体系(咱们称之为散布式体系)中时,问题的视点会发生改动,独立体系也应该依据用例进行规划。

要核算一个体系中的电器的瞬时功耗,有必要一起丈量电流和电压。

经过快速剖析,您能够用3种不同的办法来处理问题:

1)运用两个同步单通道ADC来丈量电流和电压。

2)运用一个多通道同步采样ADC,它的每个通道都或许有一个ADC,或许每个通道有一个采样坚持电路。

3)运用一个多路复用ADC,而且刺进丈量值,以补偿电压和电流丈量之间的时刻平移。

至此,您或许现已取得能够处理该问题的牢靠处理方案,可是,假如咱们扩展体系需求,从本来的单件电器辐射到整个运用,有必要丈量整个工厂中的每个沟通电源插座的功率呢?现在,您原有的瞬时功耗规划有必要散布运用于整个工厂,而且要确保其规划能够一起丈量和核算每个沟通电源插座功耗。

您现在面临的是一个散布式体系,它由一组彼此独立但又严密相关的子体系组成。每个子体系需求供给在同一时刻点采样的数据,以便核算工厂的瞬时总功耗。

最终,假如咱们继续扩展假定的运用示例,幻想一下,假如要将您的原始规划集成到国家电网之中。现在,您检测的是数百万瓦功率,任何一个链路出现问题都会导致可怕成果,例如由于压力导致的线路损坏,反过来,这又或许导致停电,形成可怕成果,例如火灾,或许医院停电。

因而,一切体系都有必要精确同步,也便是说,在整个电网中捕获的数据有必要是在同一时刻捕获,不管各数据所在的地舆状况怎么,详细如图1所示。

在这些状况下,您能够将其视为一个要害的散布式体系,且有必要从每个感知节点取得接连的、彻底同步的数据流。

与电网示例相似,这些要求也适用于航空航天或工业商场中的许多其他要害散布式体系示例。

2 奈奎斯特ADC和过采样ADC

在开端解说怎么同步多个ADC的采样时刻之前,最好先了解每个ADC拓扑怎么决议何时采样模仿输入信号,以及每种架构的优缺点。

奈奎斯特或SAR ADC:该转化器的最大输入频率由奈奎斯特或半采样频率决议。

过采样或Σ-Δ ADC:最大输入频率一般与最大采样频率成份额,一般约为0.3。

一方面,SAR ADC的输入信号采样时刻经过施加于转化开端引脚的外部脉冲进行操控。如图2所示,将一个通用转化开端信号运用到被同步体系中每个SAR ADC上,它们都会在转化起始信号的边际一起触发采样。只需确保信号之间没有显着的推迟,即转化开端脉冲在同一时刻及时抵达每个SAR ADC,体系同步就很简略完结。留意,抵达转化开端引脚的脉冲与实践采样时刻之间的传达推迟不能因设备而不同,在采样速度相对较慢的精细ADC中,这种推迟不明显。

在运用转化开端脉冲之后的某个时刻(也称为转化时刻),转化成果将经过一切ADC的数字接口显现。

另一方面,由于架构不同,Σ-Δ ADC操作也略有不同。在这种类型的转化器中,内部中心(即调制器)对输入信号采样的频率(调制器频率, f MOD )比奈奎斯特规则的最小频率高,因而它被称为过采样ADC。

经过按比严厉需求的频率更高的频率采样,能够搜集更多的样本。然后选用均匀滤波器对一切ADC数据进行后处理,原因有二:

1)每4个均匀样本,噪声下降1位。

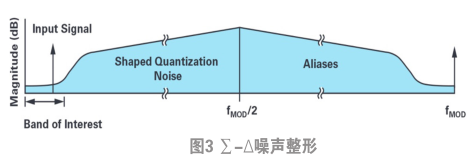

2)均匀滤波器转化函数是一个低通滤波器。当∑-∆架构将其量化噪声面向高频时,应该移除均匀滤波器转化函数,如图3所示。所以,本次滤波由这个均匀滤波器完结。

样本的均匀数量,即抽取率( N ),会决议输出数据速率( ODR ),输出数据速率是ADC供给转化成果的速率,单位为样本/秒,如式(1)所示。抽取率一般是整数,带有一组可在数字滤波器上离散编程的预界说值(即 N = 32、64、128等)。因而,经过坚持 f MOD 常量, ODR 将依据预界说值集内的 N 值进行装备。

均匀进程一般由一个sinc滤波器在内部完结,调制器的模仿转化开端脉冲也在内部生成,因而不会从外部管控转化进程触发。这种类型的转化器实践会接连采样,盯梢输入信号,并处理取得的数据。一旦该进程(采样和均匀)完结,转化器就会生成一个数据安排妥当信号,奉告操控器数据能够经过数字接口回读。

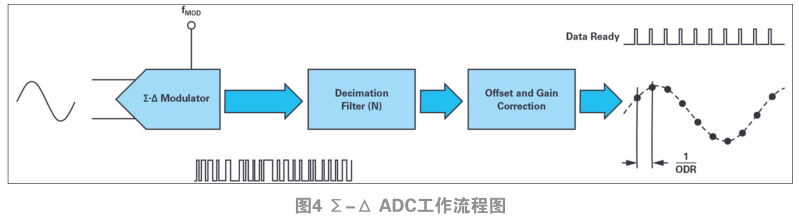

如图4所示,∑-∆的作业流程能够归纳为4个首要进程:

1)调制器以f MOD 频率对信号采样。

2)经过sinc数字滤波器对样本进行均匀。

3)对sinc滤波器供给的数据进行偏移和增益校对。

4)数据安排妥当引脚切换,表明转化成果已安排妥当,可由操控器回读。

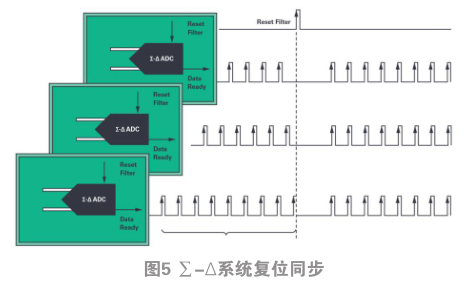

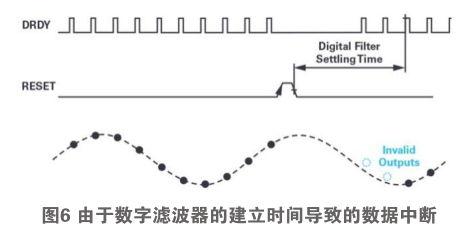

由于没有从外部操控何时触发内部采样,所以假如要对散布式体系中的多个Σ-Δ ADC进行同步,有必要一起对一切数字滤波器施行复位,这是由于均匀转化发动是由数字滤波器操控的。

图5显现在一切Σ-Δ ADC都选用相同的 ODR 和f MOD 的状况下,对同步发生的影响。

与依据SAR ADC的体系相同,有必要确保复位滤波脉冲一起抵达各个子体系。

可是,请留意,数字滤波器每次复位时,数据流都会被中止,这是由于滤波器有必要从头设置。在本例中,数据中止的继续时刻由数字滤波器的次序、 f MOD和抽取率决议。在图6显现的示例中,滤波器的LPF特性将推迟时刻,直到生成有用的输出。

3 对散布式体系同步采样的启示

在散布式体系中,大局同步信号(咱们称之为Global_SYNC)在一切模块/子体系之间同享。此同步信号能够由主体系或第三方体系(例如GPS 1pps)生成,如图1所示。

接收到Global_SYNC信号后,每个模块有必要从头同步每个转化器的瞬时采样(很或许是其本地时钟),以确保一起性。

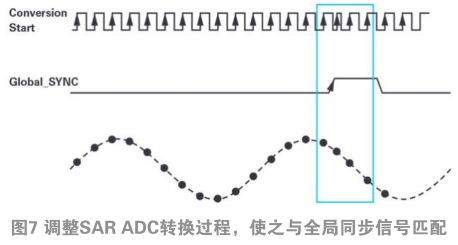

在依据SAR ADC的散布式体系中,从头同步本质上很简略,如前一节所述:本地时钟(办理转化开端信号)再次与Global_SYNC信号匹配,之后同步取得信号。

这意味着要生成频率杂散,由于在同步期间,会在不一起间和距离搜集一个样本,详细如图7高亮蓝色部分所示。在散布式运用中,这些杂散或许是能够承受的,而中止数据流在某些运用中则的确至关重要,例如前面说到的电力线监督之类的运用。

在依据∑-∆的散布式体系中,从头与Global_SYNC信号同步的进程会略微杂乱一些,这是由于调制器会继续对模仿输入信号采样,而转化进程也不像SAR ADC相同从外部操控。

要对多个依据∑-∆的散布式体系施行同步,一个简略的办法便是重置数字滤波器:丢掉搜集和存储的要在均匀滤波器上运用的一切调制器示例,而且清空数字滤波器。这意味着:依据数字滤波器的次序,它需求一些时刻才干再次确认其输出,如图5和图6所示。

数字滤波器完结设置之后,会再次供给有用的转化数据,但考虑到设置所花费的时刻,在Σ-Δ ADC上重置数字滤波器或许导致的数据中止是不行承受的。散布式体系需求从头同步的频率越高,数据流中止的次数就越多,而由于这种继续的数据流中止,Σ-Δ ADC将无法运用于要害的散布式体系中。

传统运用的最小化数据中止的办法是运用可调谐时钟,例如PLL,它能够下降大局同步频率和 f MOD 频率之间的差错。

接收到Global_SYNC脉冲后,能够选用相似以下的流程,核算Σ-Δ ADC转化开端和Global_SYNC脉冲之间的不确认性。

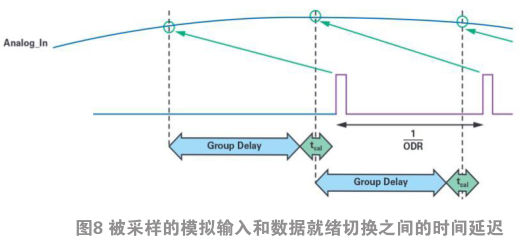

1)操控器核算采样时刻(经过了解群推迟从数据安排妥当信号向后核算,如图8所示)和Global_SYNC脉冲之间的时刻差。群推迟是一份数据手册标准,阐明从对输入采样到数据安排妥当引脚敞开(表明样本现已安排妥当,能够读取)之间的时刻距离。

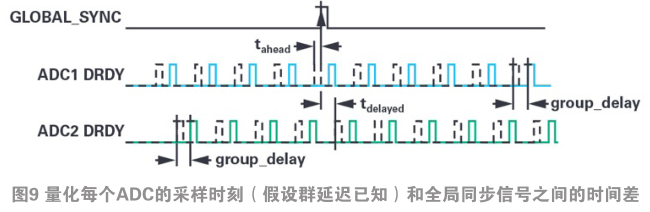

2)假如采样时刻和Global_SYNC之间存在时刻差,那么本地操控器会量化这个时刻差(t ahead 或t delayed ),如图9所示。

3)假如存在差异,能够从头设置∑-∆滤波器,或许修正 f MOD ,以便在几个采样期间调整∑-∆采样。不管哪种状况,都或许漏掉几个样本。留意,经过改动部分时钟频率( f MOD ),Σ-Δ ADC会改动其输出数据速率(ODR = f MOD /N),如此,ADC会减慢或加速对模仿输入采样的速度,以期和体系中余下的ADC和Global_SYNC同步。

4)假如 f MOD 被更新,那么在同步之后,主时钟频率会康复到本来的频率,以回来到之前的ODR,而子体系则从该时刻开端同步。

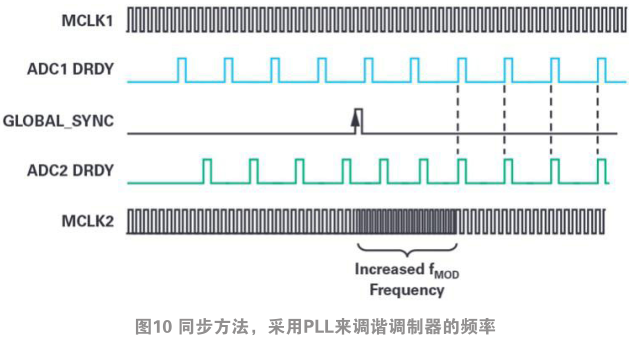

在一段时刻内改动fMOD的进程如图10所示。

这种办法在某些状况下或许不适用,由于有几个细节需求考虑:

1)将调制器频率更改为非整数倍值或许是不实践的。

2)假如能够对频率进行微调,那么改动的频率步长有必要很小,不然数字滤波器或许会超出约束,导致同步的施行时刻变长。

3)假如所需的 ODR 改动足够大,能够经过改动抽取率(N),而不是改动调制器频率(f MOD )来处理,可是,这也意味着会丢掉一些样本。

4)运用PLL意味着在到达希望的调制器频率之前,除了本身的树立时刻之外,还会额定耗费功率。

一般来说,整个体系的杂乱性和本钱会跟着体系规划的增大而添加,特别是与SAR ADC比较,关于后者,只需求将转化开端调整到与Global_SYNC信号匹配,即可轻松处理这个问题。此外,在许多状况下,由于存在上述体系约束,所以Σ-Δ ADC无法运用。

4 不中止数据,轻松从头同步Σ-Δ ADC

AD7770系列产品(包含AD7770、AD7771和AD7779)具有内置SRC。跟着这种新架构推出,固定的抽取率(N)导致的约束将不复存在。

SRC答应您选用十进制数(而不仅仅是整数)作为抽取率( N ),因而,您能够选用所需的任何输出数据速率。在之前的同步办法中,由于N是固定的,所以有必要更改外部时钟来调理f MOD,之后才干施行同步。

运用AD7770系列产品之后,N会变成可灵敏编程,以及可随时编程的值,所以无需更改f MOD ,也无需中止数据,即可对ODR编程。

这种对依据∑-∆的子体系从头同步的新办法运用SRC来简化从头同步进程,最大极限地简化了前面章节说到的杂乱性。

新办法如下:

1)接收到Global_SYNC信号之后,各子体系查看采样是否同步,以数据安排妥当信号为参阅,运用群推迟查找实践采样时刻。

2)假如采样时刻和接收到Global_SYNC信号的时刻之间存在时刻差,那么本地操控器会量化这个时刻差(tahead或tdelayed),如图9所示。

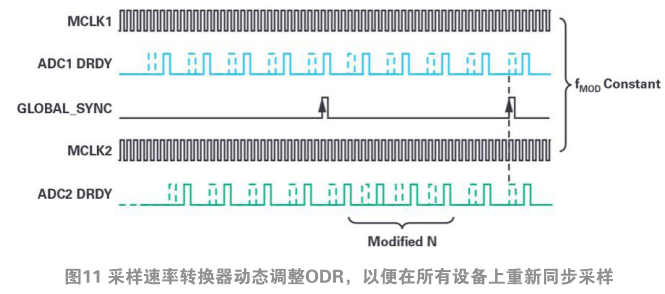

3)这时,会对一个新的 ODR 编程,使其经过SRC更改抽取率(N),然后暂时生成更快或更慢的ODR 。整个从头同步操作一般会用到4个样本(假如在AD7771上启用了sinc5滤波器,则需求6个),可是由于这些样本依然有用且彻底设置,所以不会导致数据流中止。

4)一旦接收到所需数量的DRDY,就会从头设置抽取因数,以回来所需的ODR,如此能够确保Σ-∆ ADC与其他子体系坚持同步,如图11所示,其不形成数据中止。

5 定论

要害散布式体系需求一切子体系同步进行转化,且具有继续的数据流。

SAR转化器供给一种直观的从头同步采样办法:经过从头调整转化开端信号,使其与Global_SYNC脉冲匹配。

在需求高动态规模(DR)或信噪比(SNR)的运用中,SAR不行运用,可是传统Σ-∆转化器也变得难以运用,由于这些转化器不具有灵敏性,无法在不中止数据流的状况下从头调理。

如示例所示,SRC供给了一个无缝同步例程,与其他处理方案比较,它的推迟更小、本钱和杂乱性更低。

SRC能够在许多运用中一展所长。与电力线监控示例相同,任何线路频率改动都能够经过当即动态改动抽取率来补偿。如此,确保电力线的采样频率一直共同。依照本文所示,在要害散布式体系中,SRC也可用于高效从头同步体系,不会形成数据流中止,也不需求选用额定的元器件,例如PLL。AD7770处理了对依据Σ-Δ ADC的散布式体系进行同步的传统问题,不会丢掉样本,也不会像依据PLL的办法相同,额定添加本钱和杂乱性。

本文来源于科技期刊《电子产品国际》2020年第01期第24页,欢迎您写论文时引证,并注明出处。