著作摘要

本著作为依据ATLYS FPGA开发渠道、VmodCAM双目摄像头模块开发规划的双目立体视觉体系。VmodCAM用于收集双路的视觉信息,FPGA开发渠道担任完结视觉信息的处理及图画的高速剖析。收集到得左右两路图画信息经过剖析处理,便可得到二维图画上的深度信息。深度信息的表现本著作中规划了两种方法,其一为视觉信息的立体显现,经过处理生成叠加的红蓝3D图画,给人直观上的立体感触。该规划方面可以运用于立体视觉的收集与显现,定位为立体视觉的收集与显现体系。另一方面,经过在FPGA片上规划的高速图画处理体系,可以依据左右图画的距离,计算出图画的深度信息,也便是物体在环境中相关于双目摄像头的三维坐标。该规划方面可以运用到人机交互、机器视觉范畴,作为机器对环境状况的认知设备。

FPGA开发板在本著作中的效果主要有:①装备摄像头模块,收集摄像头数据;②将图画数据缓存在片外的DDR2中;③完结图画的剖析处理;④完结图画的显现及UART数据传输。

规划方针

一方面,完结立体视觉实时收集与显现体系的规划,让人戴上3D眼镜后可以实时看到立体画面;另一方面,完结物体三维空间定位。

已完结:依据红蓝3D眼镜的立体视觉实时收集与显现;红外光点的三维空间定位。

将完结:依据偏振3D眼镜的立体视觉实时收集与显现;简略环境下的物体空间定位及环境三维重建,并开发成用于人机交互的设备。

规划总概

本规划为在FPGA片上完结的视频、图画收集与处理体系,完结三维图画的重建与数学建模。片上体系运用VHDL+Verilog联合开发,具有很高的数据处理速度。该规划的两个方面现在已开始完结,图画的收集、处理进程均由片上体系完结,为该规划的进一步优化打下了很好的根底。

开发工具

硬件方面:

- Diglient ATLYS FPGA 开发板

- Diglient VmodCAM 双目摄像头模块

- LCD 显现器

- 计算机

软件方面:

- XILINX ISE

- Digilent Adept

- Processing

布景

依据有关科学计算,人们经过视觉取得的信息量约占取得信息总量的70%。视觉信息中具有着许多有价值的信息量,可是因为视觉信息数据量大,处理进程杂乱等要素,曩昔很长一段时间中,视觉信息处理仅处于理论研究阶段。

曩昔20年间,跟着IT工业的飞速行进,软硬件方面均发生的天翻地覆的改变,这让许多杂乱的视觉信息的处理的进程变得越来越可完结化。

近几年以来,视频图画处理方向上的工程运用越来越多,并已走入大多数人的日子。比方:指纹辨认、Kinect体感器等等。

但是,现在的图画处理进程的完结大多是依据软件渠道的,如Intel开发的图画处理库OpenCV等。关于低速、简略的图画处理,软件尚能担任,但高速、杂的图画处理进程用软件处理起来很难到达实时性。鉴于这方面的原因,咱们决议选用FPGA的并行处理、流水线处理才能完结视觉信息的高速处理。

经过FPGA做视觉信息处理的进程,不断探究硬件图画处理算法。一起,图画具有的许多方面特征用并行处理方法去完结将具有明显优势,这也将是未来图画处理的一个重要发展方向。

规划介绍

榜首部分:立体视频收集与显现

- 体系组成:

1.整体框图:

本体系由从硬件上看由三大部分构成,分别是用于图画收集的摄像头模块、完结图画处理的FPGA开发板、进行成果显现的LCD显现器。

2.硬件组成部分:

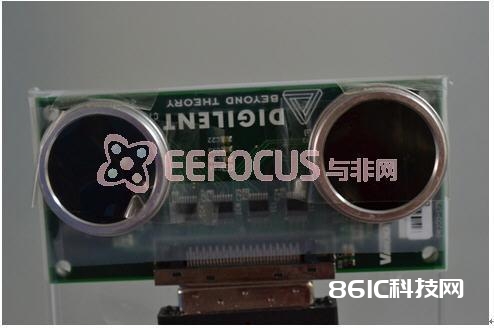

(1)摄像头模块:选用Digilent公司出品的VmodCAM摄像头模块。该模块上搭载有两个Micron公司的MT9D112 CMOS图画传感器(本体系中用到一个)。该传感器最高支撑1600×900分辨率,选用I%&&&&&%的装备协议,而且内置PLL锁相环,可以发生严厉精准相位的操控时钟,到达高速高精度的意图。

- 数据处理体系:本硬件渠道的数据图画处理,智能辨认体系由FPGA开发板完结。本项目中运用的为Digilent公司的ATLYS FPGA 开发板。其上集成的FPGA 芯片为Xilinx 公司出产的Spartan-6 LX45。该开发板上集成有多个视频输入输出接口(HDMI),适合做视频处理。

- 显现模块:咱们选用液晶显现器作为体系的显现界面,到达可视化强,便于实时的交互的效果。

- 片内体系部分:

(1)体系架构

(1)体系架构

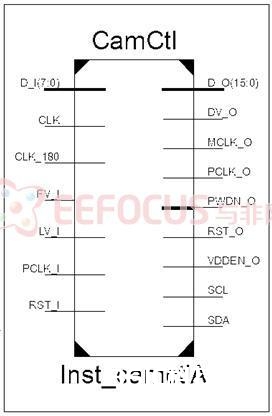

(2)摄像头模块

Input:

D_I(7:0):8-bit数据输入(data input),来自片外的摄像头模块,传输像素的值,一般两个时钟的数据(16bit)组成一个像素值;

CLK:时钟信号,来自时钟模块Inst_SysCon的CAMCLK_O输出;

CLK_180:时钟信号,来自时钟模块Inst_SysCon的CAMCLK_180_O输出(应该为CLK信号的180度相差信号,用来与CLK和谐完结D_I(7:0)到D_O(15:0)的转化,起到像素前后部分的标志位效果);

FV_I:帧有用信号(Frame Valid),也称场同步信号,来自摄像头模块,输出一帧图画期间,电平为高,帧与帧之间时,电平拉低;(拜见MT9D112_DS Page28 Figure18)

LV_I:行有用信号(Line Valid),也称行同步信号,来自摄像头模块,输出图画的一行期间,电平为高,行与行之间时,电平拉低;(拜见MT9D112_DS Page28 Figure18)

PCLK_I:信号来自CAM_PCLK_I经过I/O缓冲器(IOBUF)后的输出,逻辑上等价于CAM_PCLK_I;

RST_I:模块复位信号,来自SysCon模块的ASYNC_RST端口。

Output:

D_O(15:0):16-bit数据输出信号(RGB565),由两个8-bit的输入数据拼装得到,代表一个像素的色彩值等,输出给FBCtl图画缓存操控模块的DIA(15:0);

DV_O:输出给FBCtl图画缓存操控模块的ENA,作为使能信号,每逢一个像素的16位数值配齐时置1;

MCLK_O:输出给摄像头,作为其外部时钟信号XCLK的输入(6—54MHz);

PCLK_O:输出给FBCtl图画缓存操控模块的CLKA,来自于PCLK_I的缓冲,作为图画存储时的像素同步时钟;

PWDN_O:恒定为0,直接输出给摄像头的,起到power_up功用;

RST_O:输出给摄像头,用作摄像头复位(低有用);

VDDEN_O:与Inst_camctlB的相同端口求与后输出到摄像头的VDDEN管脚,应该是连到摄像头,作为作业接通通电源的使能信号;

SCL:输出到摄像头的SCLK端口(FPGA→Camera),作为串行接口的时钟输入;

SDA:输出到摄像头的SDATA端口(FPGA↔Camera),作为串行接口的信号传输。

(3)图画缓存操控模块

Input:

ENC:来自VideoTimingCtl模块的VDE_O端口,读写操控();

RSTC_I:来自SysCon模块的ASYNC_RST端口;

CLKC:来自SysCon模块的PCLK_O端口;

//////////////////////////////////////////////////////////////////////////////

ENB:来自CamCtlB模块的DV_O端口,读写操控(1写);

RSTB_I:来自Inst_InputSync_FVB模块的D_O端口取反与SysCon模块的ASYNC_RST端口求或;

CLKB:来自CamCtlB模块的PCLK_O端口;

/////////////////////////////////////////////////////////////////////////////

ENA:来自CamCtlA模块的DV_O端口,读写操控(1写);

RSTA_I:来自Inst_InputSync_FVA模块的D_O端口取反与SysCon模块的ASYNC_RST端口求或;

CLKA:来自CamCtlA模块的PCLK_O端口;

/////////////////////////////////////////////////////////////////////////////

ddr2clk_2x:来自SysCon模块的DDR2CLK_2X_O端口;

ddr2clk_2x_180:来自SysCon模块的DDR2CLK_2X_180_O端口;

pll_ce_0:来自SysCon模块的PLL_CE_0_O端口;

pll_ce_90:来自SysCon模块的PLL_CE_90_O端口;

pll_lock:来自SysCon模块的PLL_LOCK端口;

async_rst:来自SysCon模块的ASYNC_RST端口;

mcb_drp_clk:来自SysCon模块的MCB_DRP_CLK_O端口;

RD_MODE(1:0):来自SysCon模块的MSEL_O(1:0)端口;

DIB(15:0):来自Inst_camctlB模块的D_O(15:0)端口;

DIA(15:0):来自Inst_camctlA模块的D_O(15:0)端口;

Output:

RDY_O:该信号取反后与SysCon模块的ASYNC_RST信号求或后输给VideoTimingCtl模块的RST_I端口;

mcb3_dram_ras_n:输出给DDR2;

mcb3_dram_cas_n:输出给DDR2;

mcb3_dram_we_n:输出给DDR2;

mcb3_dram_odt:输出给DDR2;

mcb3_dram_cke:输出给DDR2;

mcb3_dram_dm:输出给DDR2;

mcb3_dram_udm:输出给DDR2;

mcb3_dram_ck:输出给DDR2;

mcb3_dram_ck_n:输出给DDR2;

DOC(15:0):输出给DVITransmitter模块的BLUE_I/GREEN_I/RED_I,以RGB565的方法自高位向低位摆放;

mcb3_dram_a(12:0):输出给DDR2;

mcb3_dram_ba(2:0):输出给DDR2;

mcb3_dram_udqs:双向端口,连接到DDR2;

mcb3_dram_udqs_n:双向端口,连接到DDR2;

mcb3_rzq:双向端口,连接到DDR2;

mcb3_zio:双向端口,连接到DDR2;

mcb3_dram_dqs:双向端口,连接到DDR2;

mcb3_dram_dqs_n:双向端口,连接到DDR2;

mcb3_dram_dq(15:0):双向端口,连接到DDR2;

- 图画处理完结:

第二部分:三维空间定位

- 硬件组成:

- 摄像头模块:在摄像头前加装了两个850nm的红外滤光片,用来滤出红外光点。

- 红外光点:

- LCD显现器:用于光点辨认的显现。

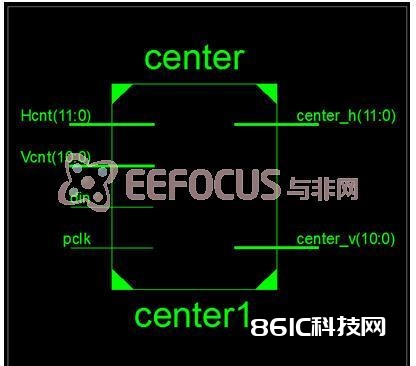

- 光点检测片上模块

模块源代码:

module center(

input pclk, // pixel clock

input din, // 1-bit pixel value, come from BW image buffer

input [11:0] Hcnt, // 0-1599 来自VideoTimmingCtl的HCNT_O

input [10:0] Vcnt, // 0-899 来自VideoTimmingCtl的 VCNT_O

output reg[11:0] center_h, // 0-1599,中点横向坐标

output reg [10:0] center_v // 0-899,中点纵向坐标

);

reg [20:0] num; //亮点区像素总数

wire [19:0] h_num; //亮点区像素总数的一半

reg [20:0] num_cnt; //亮点区像素总数计数

reg [11:0] h_cnt; //中点横向坐标计数

reg [10:0] v_cnt; //中点纵向坐标计数

reg [20:0] center_line_sum; //中心一行的有用像素横坐标和

reg [20:0] center_line_sum_cnt; //中心一行的有用像素横坐标和计数

reg [10:0] center_line_num; //中心一行的有用像素总数

reg [10:0] center_line_num_cnt; //中心一行的有用像素总数计数

assign h_num= num[20:1];

//有用区间

reg en;

always@(*) begin

if(Hcnt>0 Hcnt1599 Vcnt>0 Vcnt899)

en= 1;

else

en= 0;

end

//亮点区像素总数计数

always@(posedge pclk) begin

if(Hcnt==1 Vcnt==0) //扫描到像素点(1,0)处时

begin

num_cnt= 0;

end

else

if(din==1 en==1) num_cnt= num_cnt+1;

else num_cnt= num_cnt;

end

//中点纵坐标计数

always@(posedge pclk) begin

if(num_cnth_num) v_cnt= Vcnt;

else v_cnt= v_cnt;

end

//中心一行有用像素横坐标和

always@(posedge pclk) begin

if(Hcnt==1 Vcnt==0) //扫描到像素点(1,0)处时

begin

center_line_sum_cnt= 0;

end

else

if(Vcnt==center_v en==1 din==1)

center_line_sum_cnt= center_line_sum_cnt + Hcnt;

else

center_line_sum_cnt= center_line_sum_cnt;

end

//中心一行的有用像素总数

always@(posedge pclk) begin

if(Hcnt==1 Vcnt==0) //扫描到像素点(1,0)处时

begin

center_line_num_cnt= 0;

end

else

if(Vcnt==center_v en==1 din==1)

center_line_num_cnt= center_line_num_cnt + 1;

else

center_line_num_cnt= center_line_num_cnt;

end

//除法器

wire rfd;

wire [10:0] fractional;

wire [20:0] quotient;

div Divider (

.rfd(rfd),

.clk(pclk),

.dividend(center_line_sum),

.quotient(quotient),

.divisor(center_line_num),

.fractional(fractional)

);

//一帧结束赋值

always@(posedge pclk) begin

if(Hcnt==1598 Vcnt==899)//扫描到像素点(1598,899)处时

begin

num= num_cnt;

center_v= v_cnt;

center_h= quotient[11:0];

center_line_sum= center_line_sum_cnt;

center_line_num= center_line_num_cnt;

end

end

endmodule

- 软件部分:

PC上在Processing环境中开发了一个3D动画界面,经过立方体模仿红外光点的三维方位。该程序接纳从开发板经由UART协议发来的光点坐标,并将成果显现在窗口中。