作者/ Brian Fortman TI公司

摘要:本文剖析了将一个FPGA引进到驱动架构时所面对的应战,以及这些架构的开展前史和工业驱动操控SoC(COTS MCU)的新功用怎么改变在工业驱动中运用FPGA的本钱效益形式。

许多工业用逆变器和伺服驱动器厂商一向依靠现场可编程门阵列(FPGA)或ASIC技能来完结例如32位微操控器(MCU)等商用及现存(COTS)产品无法支撑的功用。可是,为了支撑方位传感器反应或Σ-Δ滤波,将FPGA和ASIC添加到软件可编程操控器中往往会添加体系的本钱和杂乱度。因而,咱们不由会问:被放置在FPGA中的功用真的能够为驱动产品带来差异性吗?用户是否有必要为FPGA中的功用付出额定的费用,以及包括这些功用是否现已成为每个驱动厂商的规范惯例?换句话说,它们是否仅仅是工业驱动职业中的一个筹码?

FPGA存在的坏处

尽管FPGA支撑可从头编程,而且被认为有或许供给体系适应性和更佳的体系功用,可是相关于现在MCU为工业驱动运用带来的新机遇,FPGA也有一些坏处。开发人员应该在所需专业工程技能、整体项目作业量以及体系总本钱的影响之间做出权衡。

许多驱动体系在开发中都保留了一个COTS可编程微操控器或装备FPGA的微处理器。这个处理器的C言语代码生成和调试开发环境是众所周知且有必要的。现在,将一个FPGA引进到体系中需求一个额定的开发流程和一整套东西。尽管这些东西在易用性方面取得了一些前进,通常状况下,开发MCU C言语代码以及FPGA VHDL代码的并不是同一名工程技能人员。VHDL编码风格和开发流程与MCU软件开发截然不同,而且需求专门的工程规划资源。此外,FPGA开发人员还有必要成为针对他们所履行硬件IP的初级和体系级专家。例如,他们不光需求知道怎么为一个BiSS主控完结VHDL,还需求把握BiSS协议,这是由于他们需求验证规划的FPGA完结方法契合BiSS传感器的要求。这个专业化的工程规划技能组合或许并不是每一个运动操控或逆变器厂商都能够为其职工供给的,而且它也必定会为完结运动和电机操控功用等差别化特性带来额定的作业量。那么,只运用一个自身就支撑BiSS编码器的微操控器是不是相对更简略一些呢?

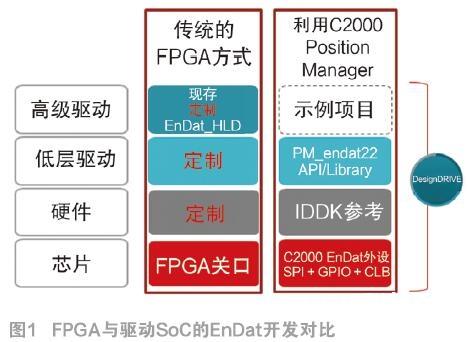

从开发视点来看,产品司理实际上需求将FPGA的生成视为一个定制开发。关于经过FPGA为商场供给的产品特性,他们的开发团队具有额定的所有权,一起要承当更大的职责。假如VHDL的编码不正确,他们不能求助于FPGA供货商,只能自己查找问题的本源,一起寻求弥补所需的资源。当把这种状况与运用COTS MCU的形式比较较时,与FPGA开发相关的定制职责远远超过了在FPGA规划的逻辑门。印刷电路板 (PCB)、MCU逻辑门级接口和寄存器接口、软件笼统与整体体系集成作业全都是非规范的,也便是说,全都不是现成可用的解决方案(如图1)。除了开发,这个形式会跟着全新对接组件的推出或修正而在用户支撑、产品维护更新和长时刻合规方面添加额定的工程规划杂乱性。所以,运用一个具有这些特性的规范MCU,而且让供货商对整个产品解决方案的硬件、软件、东西与规划担任,使问题变得更简略。

接下来,最显着的一点或许便是额定组件关于物料清单的影响。FPGA本钱不只会影响单价,FPGA器材将需求额定的PCB面积以及用于MCU对接和电源的引脚。这些本钱在运用FPGA时是无法防止的。不过,当这些功用现已存在于驱动SoC MCU之上时,也就不需求这些本钱开销了。经过数个实例的比较,咱们发现,与驱动SoC器材比较,运用FPGA需求额定且愈加杂乱的电源电路。此外,履行FPGA会在体系中引进没有必要的逻辑门,比方衔接MCU的寄存器接口以及衔接完结相位电流和电压感测的外部模数转换器(ADC)接口。一个SoC驱动包括一个针对驱动运用的高功用ADC,而且不需求这个额定的逻辑电路。所以,相关于根据FPGA架构的MCU,运用单个COTS驱动SoC能够有更多时机削减整体体系本钱。

COTS MCU解决方案

那么,FPGA是怎么成为逆变器驱动架构中的常见作法的呢?当运用COTS MCU无法完结全新的体系功用时,许多开发人员有必要履行他们特定的PWM/IGBT维护机制,比方在MCU以外进行处理。别的一些开发人员或许觉得他们当时的守时回路太短,无法由一个可编程MCU进行处理,有必要在逻辑门内完结。一旦在体系中运用了FPGA,它自可是然地就成为了集成对持续开展商场中全新技能支撑的器材。例如,FPGA集成了顺时针/逆时针(CW/CCW)和脉冲串输出(PTO)端口,以完结与PLC和运动操控器的通讯。接下来,FPGA开端支撑新呈现的规范以及比如EnDat和BiSS等专有方位传感器。从而,针对阻隔式Σ-Δ ADC中已调制输出的滤波电路也被集成在FPGA器材内。此外,有少量几个工业以太网规范的MAC操控器也支撑FPGA逻辑门。

尽管某些驱动功用的扩展正在变成FPGA的一部分,但也呈现了一个风趣的新状况。一些COTS操控器开端在片上供给这些功用,而且能够为任何驱动开发人员创造呈现成可用的功用。这儿面的差异是很明显的:片上功用能够当即供给给开发人员,换言之,只需购买产品组合中的一个MCU,就无需经过FPGA来自己构建这些解决方案。正因如此,开发人员现在能够防止以上提及的大多数坏处。

具有DesignDRIVE技能的C2000TM MCU便是一款COTS MCU,能够供给这个更高等级的驱动体系集成。整个产品的规划意图在于经过下降对专门工程规划人才的需求、节约开发时刻以及简化体系本钱,协助驱动开发人员从中获益。

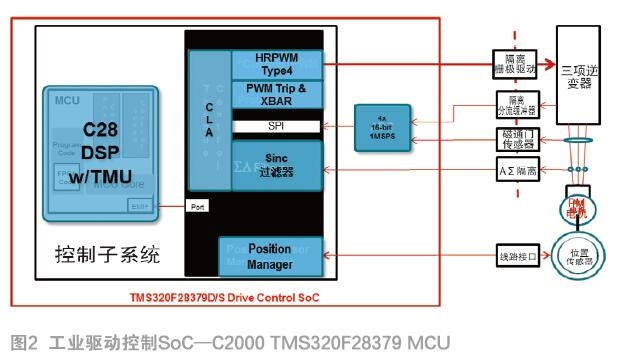

现在,C2000 DelfinoTM MCU工业驱动片上体系(SoC)能够处理以下使命,而这些使命之前一向在FPGA中完结,例如,快速转矩环路核算、Σ-Δ ADC信号过滤、高功用PWM、PWM维护以及与高功用方位传感器的对接。Delfino MCU产品组合能够完结低于3微秒的浮点转矩环路核算,而且包括高度灵敏的150ps高分辨率PWM。这个CLA实时协处理器担任处理这些算法,以最大极限地削减采样与下一个PWM指令之间的距离。此外,片上还有多达8通道的集成Σ-Δ滤波器,一起,在同一条通道上还具有平行规模比较器。片上比较器子体系和PWM区间功用能够在50ns内调用至安全的PWM状况(例如封闭)。Delfino MCU在为触发区间事情而生成片上条件时十分灵敏。许多不同类型的PWM维护概念能够运用这些片上资源完结,而且因而也就无需将电路放置在外部的FPGA中。驱动体系概览如图2。

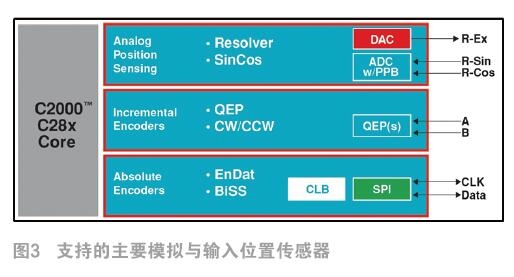

此外,这款全新的Delfino TMS320F28379S和TMS320F28379D MCU以及DesignDRIVE方位管理器技能是Delfino MCU系列的最新成员。经过将DesignDRIVE方位管理器软件与全新的Delfino F28379 MCU组合在一起,上述所说到的片上功用得到了扩展,用于完结与EnDat2.2和BiSS-C肯定方位传感器的轻松、直接衔接,这都是之前需求FPGA才干完结的功用。不只如此,经过运用某些精细片上模仿电路,同样是这些器材,它们能够解码解算器信号以及来自SIN/COS换能器的视点。

这款解决方案能够供给广泛的方位传感器支撑、灵敏性、可扩展性和稳健耐用性,协助开发人员经过削减FPGA或AS%&&&&&%电路板面积来下降体系本钱。

C2000 DesignDRIVE技能为工业驱动供给了片上解决方案,集成在COTS实时MCU内部。DesignDRIVE解决方案简化了体系、节约了电路板空间和开发作业量,这使得开发人员不必在业界非差别化特性方面做出没有必要的投入。反之,开发人员能够将注意力放在产品差别化以及中心竞争力方面,比方说电机操控和运动操控,无需建立FPGA或编写那些完结非差别化使命所需的杂乱代码。

本文来源于我国科技期刊《电子产品世界》2016年第10期第31页,欢迎您写论文时引证,并注明出处。