摘要 PCI Express是一种高功用互连协议,被广泛运用于网络适配、图形加快器、网络存储、大数据传输以及嵌入式体系等范畴。文中介绍了PCIe的体系结构,以及运用Altera Cyclone IV GX系列FPGA完结PCIe接口所触及的硬件板卡参数、运用层体系计划、DMA裁定、PCIe硬核装备与读写时序等内容。

PCI Express(PCIe)是一种高功用互连协议,可运用于网络适配、图形加快、服务器、大数据传输、嵌入式体系等范畴。PCIe协议在软件层上可兼容于PCI和PCI—X,但一起也有显着的不同。在两个设备间,其是一种依据数据包、串行、点对点的互连,因而所衔接设备独享通道带宽。依据运用的版本号和通道数,其功用具有可扩展性。关于PCIe 2.0,每条通道在每个方向上的数据传输速率是5.0 Gbit·s-1。从PCIe×1~PCIe×16,能满意必定时间内呈现的低速设备和高速设备的需求。

Altera供给了兼容于PCIe 1.0和PCIe 2.0的解决计划,无论是作为根节点仍是端点,都可以经过嵌入在FPGA内部的可装备硬核IP模块完结,而不占用可编程资源,这既节省了资源也提高了运用的可靠性。Altera的IP编译器可以供给×1,×2,×4,×8的通道接口。本文首要介绍选用Cyclone IV GX系列的FPGA来完结×4的PCIe接口所触及的硬件电气规范、协议规范等。

1 PCIe总线体系和Cyclone IV GX

1.1 PCIe总线体系概述

PCI Express是一种依据数据包、串行、点到点的高功用互连总线协议。其界说了一种分层的体系结构,包含软件层、处理层、数据链路层和物理层。其间软件层是坚持与PCI总线兼容的要害,PCIe选用与PCI和PCI—X相同的运用模型和读写通信模型。支撑各种常见事物,如存储器读写事物,IO读写事物和装备读写事物。并且因为地址空间模型没有改动,所以现有的操作体系和驱动软件无需进行修正即可在PCIe体系上运转。此外PCIe还支撑一种称为音讯事物的新事物类型。这是因为PCIe协议在取消了许多边带信号的情况下,需求有代替的方法来告诉主机体系对设备中止,电源办理,热插拔支撑等进行服务。

1.2 Altera Cyclone IV GX系列FPGA

Cyclone IV GX FPGA选用Altera老练的GX收发器技能,具有拔尖的颤动功用和优异的信号完整性。运用灵敏的收发器时钟体系结构,可充分运用收发器一切可用资源,完结多种协议。Cyclone IV GX FPGA为根端口和端点装备的PCI Express×1、×2和×4供给仅有的硬核知识产权(IP)模块。因而不必再接入其他专用的PCIe协议芯片,即可完结端到端的高速数据传输。

Cyclone IV系列的FPGA还支撑一系列外部存储器,包含DDR2 SDRAM,DDR SDRAM,QDR SDRAM。Altera可供给速度最快、功率最高、最低推迟的存储器操控器,使得FPGA可以接入现有的更高速的存储器材。专用的DQS和DQ引脚在芯片级的布线上进行优化以削减颤动和增大余量上,且固定在芯片四周的特定方位。高速外部存储器在很多运用中是重要的体系组成部分,如视频图画处理,数据通信与存储,以及DMA等。

2 板级体系和部分走线阻抗

2.1 板级体系

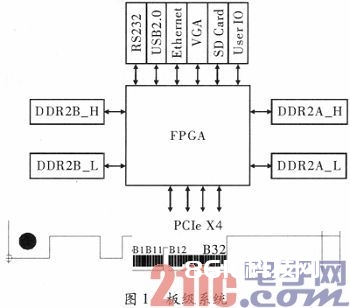

充分运用FPGA左右两边的存储器接口,别离挂两片Micron的DDR2 SDRAM颗粒,作为DMA缓存。FPGA的下侧是高速收发器接口,共有4组GXB[3:0],别离经差分链路接入PCIe ×4金手指。其间GXB[3:2]是复用接口,经过改动T节点的耦合%&&&&&%,可接入两路高速ADC。FPGA上侧接口包含USB PHY、千兆以太网PHY、串口、SD卡以及VGA接口等。FPGA有3个时钟输入,别离是:(1)来自PCIe接口的参阅时钟PCIE_REFCLK。(2)来自专用时钟模块的GXB_REFCLK。(3)来自25 MHz有源晶振的SYM_CLK。

2.2 要害走线的阻抗操控

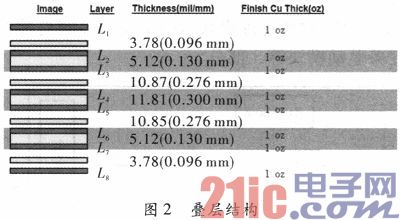

图2是PCB叠层结构示意图,其间L1,L3,L6,L8是信号层;L2,L7是地层;L4,L5是电层。信号层别离参阅接近的地层或电源层。其间PCIe链路仅在L1和L8布线,依据以上叠层结构,确认PCIe接口的100 Ω差分阻抗走线的线宽和线距离别离为4 mil(1mil=0.0254 mm)和8.1 mil,差分线长容差在5 mil之内。

DDR2 SDRAM的布线依照SSTL_18规范,DQ/DQS信号在L3和L6层,确认50 Ω单端走线线宽5.3 mil,等长操控在10 mil之内。时钟走线是100 Ω差分阻抗,布线时放在顶层和L6层。在时钟走线过孔邻近打上接地过孔,作为信号回流途径,以尽量削减阻抗不接连对信号完整性形成的影响。

3 PCIe运用层规划计划及仿真

3.1 PCIe IP核结构

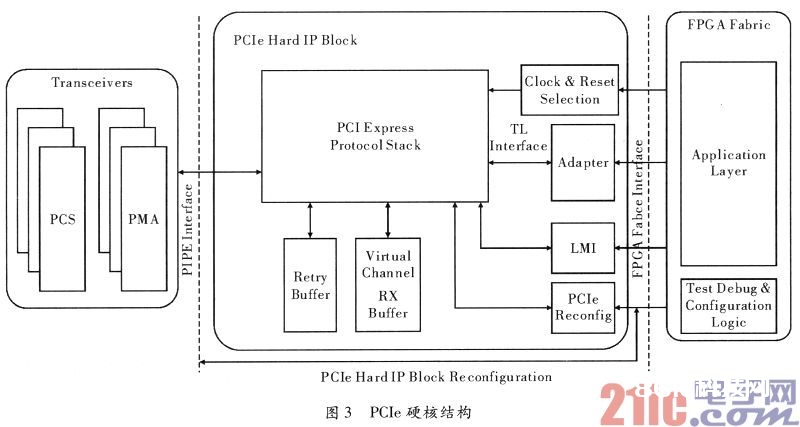

Altera的PCIe硬核IP包含处理层,链路层和物理层所要求的悉数功用,以及大多数的可选功用。只需在IPCompiler中经过简略的参数设置即可生成全功用的IP模块,如果是作为端点设备,可以运用Avalon-ST接口或Avalon—MM接口适配器,将运用层映射为处理层的TLP。Avalon—ST适配层将运用层的Avalon—ST接口映射到PCIe处理层的TLPs。

3.2 运用层规划

图4左边是运用层的计划图,首要包含装备模块、硬核IP模块、时钟办理模块、DMA读写操控与裁定模块、使命驱动模块等5部分。

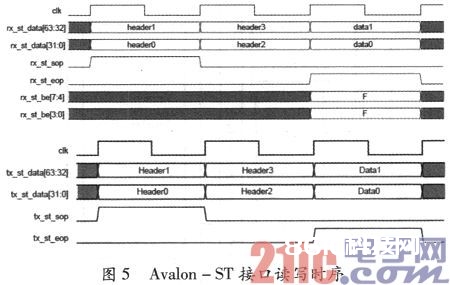

规划选用64位Agalon—ST接口,这样供运用的层运用的时钟pld_clk与内核时钟同频。TLPs分为Header、PayLoad和ECRC 3部分。其间TLP的数据包头指出了数据包的类型,路由方法,有效载荷长度,方针地址,设备ID,功用ID,总线ID等内容,而数据包后还可生成与校验有关的ECRC信息,这些特征均有助于增强传输过程中数据的完整性与可靠性。图5是一个以4双字长度为例的数据接纳的时序图,其间rx_st_data和tx_st_data标明64位宽度的读写数据端口,rx_st_sop和tx_st_sop标明数据包开端标志,rx_st_eop和tx_st_eop标明数据包完毕标志。运用层可依据这些数据和标志位完结TLP接纳与发送同步。

规划中还包含链式DMA,用于FPGA外部存储与体系存储器的数据传输。经过DMA拜访外部存储器的最大优势在于,CPU装备完DMA状况机后可持续履行其他指令操作,然后DMA状况机遇经过恳求PCIe总线中止的方法来完结数据传输。在用DMA时需求设置两个基址BAR2和BAR3最小为256 Byte。DMA首要分为读操作、写操作以及裁定3部分。初始条件下,DMA处于复位状况,经过读取DMA信息标明符来判别当时是否处于闲暇状况,并从FPGA内部读取DMA操控信息,并相应的进入读操作或写操作。以CPU写FPGA外部存储器为例,CPU经过PCIe总线写BAR0地址数据来装备并敞开DMA Engine。FPGA将宣布对CPU的DMA读恳求,然后等候CPU发送DMA数据。此刻DMA Engine处于WAIT_FOR_DATA状况,等候来自PCIe接口的DMA数据包。相同,CPU读FPGA外部存储器时,FPGA将宣布对CPU的DMA写恳求,并当DMA完结读操作后,等候PCIe接口发送DMA数据包,并由中止标志位判别是否敞开PCIe中止。状况搬运如图6所示。

在端点存储器方面,2片16位的DDR2 SDRAM并接构成一个32位的FPGA片外存储器,并依据DDR2SDRAM芯片手册在Altmemphy导游中装备好相关时序与推迟参数,即可生成DDR2 SDRAM操控器。在做电路图规划时,因为引脚驱动才能的问题,要害是FPGA对DDR2 SDRAM的引脚在接连的区域内不能超过必定数量,最好能束缚引脚区域,全编译一遍后由软

件自在分配,再由人作业恰当调整,直到没有严峻正告。

3.3 数据收发仿真测验

当用PCIe IP Compiler创立一个PCIe的硬核IP时,会生成一个用户可修正的测验文件顶层以及根联合体模型。这样就对测验运用层接口功用供给了一个简略的途径,只需在测验文件中做一个模块例化,即可构建一个简略的PCIe体系测验渠道。

如上共15个寄存器,其间tl_cfg_add和tl_cfg_ctl别离标明要更新的寄存器地址和对应的寄存器数据,tl_cfg_sts是装备的状况。运用tl_cfg_ctl_wr和tl_cfg_sts_wr的跳变边缘,由此可知对应寄存器的内容已产生更新,以此来确认数据的安全采样机遇。

如上信号tx_st_sop0的跳变启动了一个TLP数据包的开端。运用层参阅tx_stream_read0信号开端往数据端口写入数据,其间前两个数据是TLP的包头。分解成双字格局为:0x40000020,0x010800ff,0x000001880和0x00000000。即这是一个32位地址的写存储器TLP,数据长度为32双字。当tx_stream_read0变为低电平2个周期后应中止写入数据,直到tx_stream_read0再次变为高电平2个周期后可持续写入数据。

如上信号rx_st_sop0呈现高电平标明一个TLP数据包的开端。rx_st_data0的前两个数据是TLP的数据包头,分解为双字后是:0x4a000020,0x00000080,0x01080270和0x000 00000。由这些包头信息可知这是—个带数据的完结TLP,完结者ID是0x0000,恳求者ID是0x0108。且这以后含有32个双字的数据,第一个双字是0xaaa00001,第二个双字是0xaaa 0002,直到0xaaa0020。rx_st_eop0在最终一个数据0xaaa0020aaa001f呈现时产生跳变,标明TLP数据包完毕。

4 完毕语

仿真结果标明,运用Altera Cyclone IV GX系列FPGA建立的PCIe接口可以方便地完结高速数据传输运用。跟着器材的开展和IP核的开发,多通道的PCIe总线技能将会迅速开展,并对大数据、高速数据供给安全可靠的传输管道。