软件无线电的中心思维便是将宽带A/D尽可能地接近射频天线以便将接纳到的模拟信号尽可能早地数字化,尽量在一致的硬件渠道上经过不同的软件来完结无线电台的各种功用。直接在射频端完结信号的数字化,现有的器材底子无法满意后续处理要求,特别是关于直接序列扩频数字接纳机。现在一般选用中频数字化计划,后端的中频数字信号处理单元选用可重构性的器材完结信号的处理,体系保留了软件无线电接纳机的通用、灵敏、敞开等长处。

AD6620是美国AD公司最近推出的一种数字接纳信号处理芯片,功用强大,特别适合于高速信号数字下变频的完结。

1 AD6620芯片

AD6620主要有如下特征:16位线性比特补码输入(另加3bit指数输入);单信道实数输入方式最大输入数据速率高达67MSPS,双信道实数输入方式与单信道复数输入方式最大输入数据速率高达33.5MSPS;具有可编程抽取FIR滤波器与增益操控,抽取率在2~16384之间可编程;输出具有并行、串行两种输出方式,并行方式为16比特补码输出。

AD6620的原理框图如图1所示。内部信号处理单元由四个串联单元组成,分别为:频率改换单元、二阶固定系数梳状滤波抽取滤波器(CIC2)单元、五阶固定系数梳状滤波抽取滤波器(CIC5)单元和一个系数可编程的RAM系数抽取滤波器(RCF)单元。

1.1 频率改换器

频率改换器的作用是完结数字下变频(DDC),频率改换器由两个16bit乘法器和32bit的数控振动器(NCO)组成,数控振动器发生的本振信号频率分辨率可达Fsamp/232,可发生(-Fsamp/2~+Fsamp/2)的本振信号。NCO运用数字频率合成器(DDS),由频率操控字寄存器、相位操控字寄存器、相位累加器和正弦查找表组成,能够灵敏地操控本振信号的振动频率和初始相位。

为了进步NCO的杂散功用,AD6620供给了相位颤动与起伏颤动选项。

1.2 CIC2抽取滤波器

CIC2滤波器是一个固定系数抽取滤波器,最高输入数据速率为67MHz。抽取率的取值规模为1~16的整数。当体系时钟fCLK是输入数据速率的两倍或更多倍时,能够经过设置屏蔽此作业模块,不然最小只能设置为2。

1.3 CIC5抽取滤波器

CIC5是一个5阶固定参数抽取滤波器,它的滤波特性曲线比CIC2的更为峻峭。CIC5抽取滤波器的抽取率能够取1~32规模的任何整数值。当抽取率为1时,CIC5被屏蔽。

1.4 RAM系数滤波器

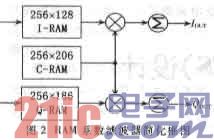

RAM系数滤波器是AD6620中终究一个信号处理功用模块?它是一个积和方式的、系数可编程的滤波器,简化框图如图2所示。

数据存储器I-RAM、Q-RAM存储了256个有C%&&&&&%5滤波器输出的最新复数位采样值,数据位宽度为20Bit。在同一个时钟周期,I路和Q路能够运用相同的系数作为滤波器系数进行核算,也能够选用不同的系数进行核算。I、Q路累加器输出数据位宽为23bit。抽取率能够取1~256的整数值。

2 AD6620作业参数的装备

AD6620的初始化能够由外部操控单元经过AD6620的微处理器接口进行,完结作业方式、NCO参数、滤波器参数等的设置。外部操控单元还能够经过微处理器接口对AD6620内部寄存器进行动态的读写,完结对AD6620的动态实时操控。外部操控单元依据AD6620的输出成果,经过对AD6620进行动态的操控,完结输入输出信号起伏、NCO频率与相位的调整,完结载波同步以及自动增益操控。

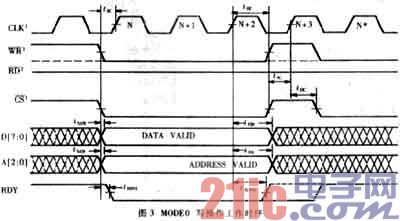

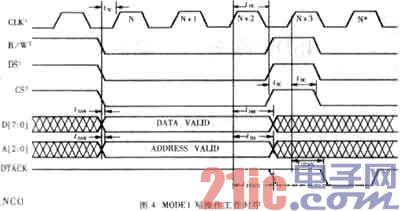

AD6620的微处理器接口有两种方式:MODE0与MODE1,二者能够经过mode的管脚进行挑选。在MODE0方式下对内部寄存器进行写操作作业时序如图3所示。

当一个写操作履行时,RDY在WR和CS变低后当即变低,直到写数据完结后的第一个时钟的上升沿再变高。在写完一个数据后,CS有必要变高后,才干进行下一个数据的写操作。在MODE1方式下对内部寄存器进行写操作作业时序如图4所示。R/W和DS变低后?开端履行一个写操作时,DTACK在数据现已被锁存后当即变低,直到DS信号变高后DTACK才变高,完结一个写操作。

初始化时假如外部操控单元挑选的时钟比AD6620的主时钟低,则对时序的要求较低,外部操控单元与AD6620的主时钟并不要求同步。如外部操控单元挑选的作业时钟比AD6620的主时钟高,则对时序的要求很高,有必要留意二者的同步联系,或许外部操控单元进行操作时要刺进一些等候周期。

3 详细使用剖析

在某类型的通讯与定位体系中,选用AD6620与FPGA构建了直扩数字化接纳机的渠道,其间频数字化处理单元的组成框图如图5。其间AD6620完结数字中频信号到零中频的搬移,FPGA完结伪码的捕获、盯梢以及信号的解调,FPGA的挑选可依据详细需求挑选Xilinx公司的Vertex-E系列芯片。一起FPGA要依据AD6620的输出成果对AD6620中数控振动器NCO的载波频率操控字、相位操控字进行修正,完结载波同步。89C51操控单元完结AD6620 的初始化,一起还能够对AD6620动态实时地进行参数调整,完结自动增益的操控。

89C51操控单元的作业时钟比AD6620的作业时钟要低得多,初始化时对二者的时钟同步没有什么特殊要求。而FPGA内部的作业时钟要比AD6620的主时钟高得多,故在对AD6620中数控振动器NCO的载波频率操控字、相位操控字进行修正时,体系在FPGA宣布操作指令后需求刺进若干等候周期,以确保二者之间正确的时序联系,完结FPGA对AD6620内部操控字的正确修正。

试验标明, 选用AD6620完结高速数字直扩接纳机的数字下变频,可有效地下降设备的复杂性、缩短开发周期,进步设备的稳定性、可靠性和灵敏性。根据AD6620与FPGA构成的中频数字化直扩接纳机已开始完结了通用数字化接纳机的功用,为终究完结软件无线电奠定了根底,具有宽广的使用远景。