Zynq SoC架构的首要优势之一便是能够经过在器材的可编程逻辑内构建外设来加速处理速度。

这是Adam Taylor 方案编写的Zynq-7000 All Programmable SoC实际操作教程系列的第三部分。前两部分教程别离刊登在《赛灵思我国通讯》第47期和48期。Adam 常常为《赛灵思我国通讯》撰稿,一起他还为All Programmable 星球社区编撰博客 ( )。

赛灵思 Zynq™- 7000 All Programmable SoC真实的重要优势之一便是能够经过在可编程逻辑(PL)侧构建外设来进步器材处理体系(PS)侧的功用。开始您或许会以为这将是一项比较杂乱的作业,可是,创立自己的外设其实很简略。

假如您企图进步PS的功用或许运用PS来操控PL侧的规划行为,那么在PL内增加外设会起到很大的协助。例如,PS或许会运用一系列存储器映射寄存器来操控PL内的规划运转或选项。

咱们挑选一种简略模块作为规划实例,该模块用于翻开和封闭ZedBoard上的存储器映射LED。咱们将运用赛灵思PlanAhead™、XPS和软件开发套件(SDK)东西分三步来创立该模块。

1. 在嵌入式开发套件(EDK)环境中创立模块。

2. 为模块编写VHDL程序并构建体系。

3. 编写运用最新定制模块的软件。

在EDK中创立模块

要创立自己的外设,首要需求从包括Zynq SoC规划的PlanAhead项目中翻开Xilinx Platform Studio (XPS) ,并挑选菜单选项中的“hardware-》create or import peripheral” 。

对咱们的实例模块而言,ZedBoard上的7个LED应展示出walking display的作用,除了最重要的那个LED必须在软件运用操控下点亮以外,其他都能够顺次相继点亮。虽然这并不是最棒的定制模块运用,但关于流程演示 而言是一种十分有用且简略的实例。一旦把握了这个流程,您将把握完成更杂乱模块所需的悉数常识。

创立外设时只需相继翻开10个简略窗口并挑选所需的选项。

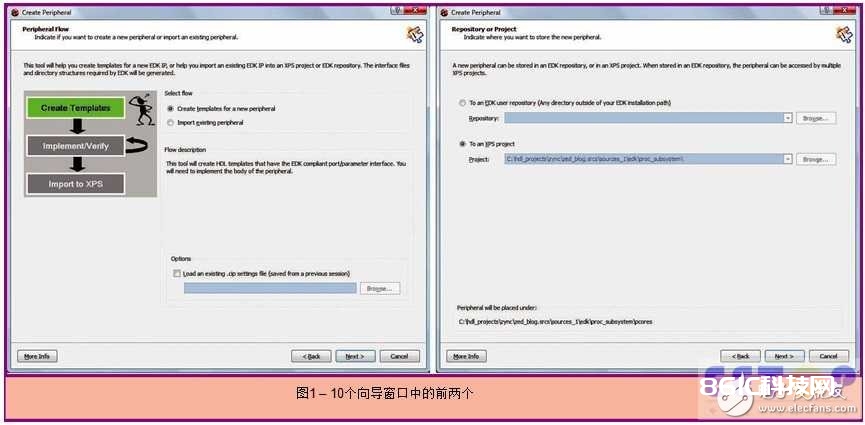

前两个截屏(如图1所示)问询是否需求创立外设或导入现有的外设,假如是,需求将其相关到哪个项目。下一步,您可在第三个截屏中对模块进行命名并高效地界说版别和修订版别。(留意:可利用外设流程底部的选项经过回读*.cip文件来从头定制已创立的模块。)

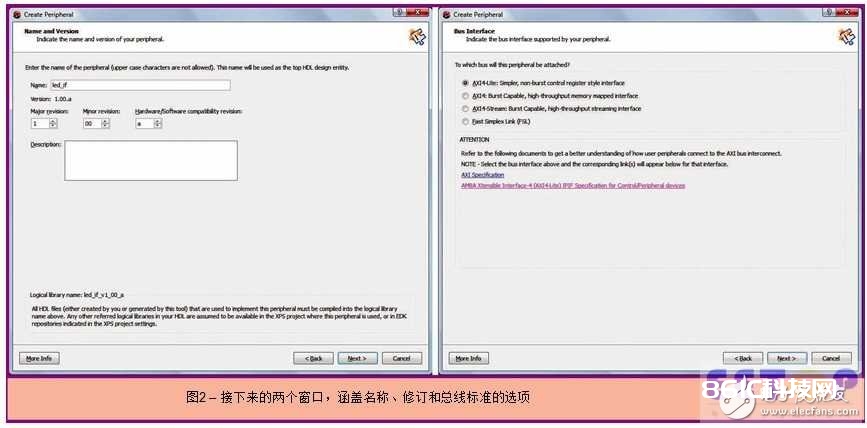

选定模块称号后,接下来要挑选所需AXI总线类型,如图2所示。咱们的实例规划需求的是一种简略的存储器映射操控寄存器型接口,因而咱们挑选了最上面的AXI4-Lite选项。(如需了解有关不同AXI总线类型的更多信息,敬请拜访: mentaTIon/white_papers/wp379_AXI 4_Plug_and_Play_IP.pdf )。在这个过程中将创立很多简略寄存器。咱们可利用处理体系经过AXI总线对寄存器进行读/写操作。

这些寄存器坐落Zynq SoC上的可编程逻辑架构中,因而也能经过用于创立外设功用的用户逻辑运用来拜访。

接下来的六个截屏为您供给相应选项,以便对AXI的主装备或从装备以及您将用于操控用户逻辑和支撑文件的寄存器的数量进行定制。本例中咱们仅运用一 个寄存器,并将其用作AXI-Lite的从装备。简化体系开发的最重要办法是挑选外设完成支撑标签上的“generate template driver files”选项。这样就能供给一系列有助于所创外设内部通讯的源文件和头文件。

最终一步,XPS会生成一系列有助于创立和运用新外设的文件:

• 以您的外设命名的顶层VHDL文件

• 可在其间创立用户逻辑的VHDL文件

• 微处理器外设描绘文件:用于界说衔接模块的接口,以便将模块与XPS合作运用

• CIP文件:必要时可对外设进行从头定制

• 针对SDK的驱动程序源文件

• 针对SDK的实例源文件

• 微处理器驱动程序界说文件:详细描绘外设所需的驱动程序

这些文件将在PlanAhead源目录(即本例中的zed_blog.srcs\ sources_1\edk\proc_subsystem)下创立。

源目录的子目录是包括XPS和PlanAhead所需文件(在与外设同名的目录下)的Pcores目录以及包括SDK所需文件的驱动程序目录。

创立RTL

在Pcores目录中您能够看到两个文件,其间一个与您所创立的组件同名(本例中为led_if.vhd),另一个文件名为

user_logic.vhd。您可在user_logic.vhd这个文件中进行规划创立。一起您将会发现导游现已帮您生成了用于经过AXI总线在此文 件中进行通讯所需的寄存器和接口。此外,您可在led_if.vhd文件进行用户逻辑模块实例化。因而,对user_logic.vhd实体所做的任何修 改都必须传送到端口映射中。假如要求运用外部端口(例如咱们的规划实例就需求外部端口来点亮LED),还必须传送对led_if.vhd实体所做的修正。

逻辑规划创立完成后,您或许期望对逻辑进行仿真以保证到达预期作用。在Pcores/devl/bfmsim目录下为您供给了总线功用模型。