一、P0口特性:

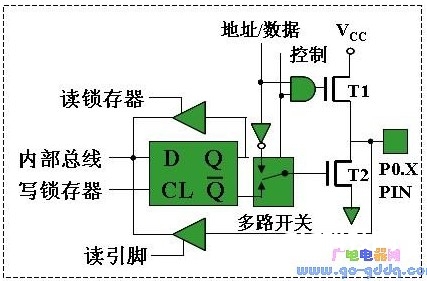

1、P0口的输出驱动器中也有一个多路电子开关。输出驱动器转接至口锁动器的Q端时,P0口作为双向I/O口运用。

这时,CPU发来的操控信号为低电平,使输出驱动电路的上拉场效应管T1截止。P0口的锁存器为“1”时,输出驱动器中的两个场效应管均截止,引脚浮空;因为P0口输出电路是漏极开路的电路,有必要外接10kΩ拉高电阻才干有高电平输出。而写入“0”时,下管导通输出低电平。

2、当输出驱动器转接至地扯/数据时,P0口作为地址/数据总线口运用,分时输出外部存贮器的低8位地址A0~A7和传送数据D0~D7。低8位地址先由地址答应锁存信号ALE锁存到外部的地址锁存器中,接着P0口便输入/输出数据信息。P0口输出的低8位地址来源于PCL、DPL、R0、R1等。

二、P0口运用方法

P0口为三态双向I/O口,当用作输进口时,一般接10kΩ左右的拉高电阻。下图所示的8751根本体系中,将一个开关K0接至P1.0和P0.0的电路有所不同,其原因是P1口内部具有拉高电阻,P0.0有必要外接拉高电阻,才干使开关K0闭合时读P0.0引脚为0,K0断开时读P0.0引脚为1。