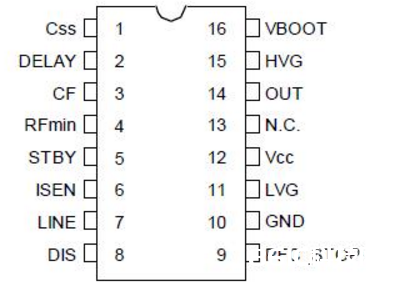

l6599d引脚图

l6599d引脚电压

L6599D引脚功用

1.Css:软发动端。此脚与地(GND)直接一只电容Css,与4脚(RFmin)直接一只电阻Rss,用以确认软发动时的最高作业频率。当Vcc(12脚)《UVLO(低电压闭锁),LINE(7脚)《1.25V或》6V,DIS(8脚)》1.85V(制止端),ISEN(6脚)》1.5V,DELAY(2脚)》3.5V,以及当ISEN的电压超越0.8V或长期超越0.75V时,芯片封闭,电容器Css经过芯片内部开关放电,以使再发动进程为软发动。

2.DELAY:过载电流推迟关断端。此端对地并联接入电阻Rd和电容Cd各一只,设置过载电流的最长持续时刻。当ISEN脚的电压超越0.8V时,芯片内部将经过150uA的恒流源向Cd充电,当充电电压超越2.0V时,芯片输出将被关断,软发动电容Css上的电也被放掉。电路关断之后,过流信号消失,芯片内部对Cd充电的3.5V电源被关断,Cd上的电经过Rd放掉,至电压低于0.3V时,软发动开端。这样,在过载或短路状况下,芯片循环往复地作业于间歇作业状况。(Rd应不小于2V/150uA=13.3kΩ。Rd越大,答应过流时刻越短,关断时刻越长。)

3.CF:守时电容。对地间衔接一只电容Cf,和4脚对地的RFmin合作可编程振动器的开关频率。

4.RFmin:最低振动频率设置。4脚供给2V基准电压,而且,从4脚到地接一只电阻RFmin,用于设置最低振动频率。从4脚接一只电阻RFmax,经过反应环路操控的光耦接地,将用于调整交换器的振动频率。RFmax是最高作业频率设置电阻。4脚―1脚―GND间的RC网络完成软发动。

5.STBY:Standby,间歇作业形式门限(《1.25V)。5脚受反应电压操控,和内部的1.25V基准电压比较,假如5脚电压低于1.25V的基准电压,则芯片处于中止状况,而且只需较小的静态作业电流。当5脚电压超越基准电压50mV时,芯片从头开端作业。这个进程中,软发动并不起效果。当负载降到某个水平之下(轻载)时,经过RFmax和光耦(拜见结构图),这个功用使芯片实施间歇作业形式。假如5脚与4脚间没有电路相关,则间歇作业形式不被启用。

6.ISEN:电流检测信号输入端。6脚经过电阻分流器或容性的电流传感器检测主回路中的电流。这个输入端没有计划完成逐周操控,因而有必要经过滤波取得均匀电流信息。当电压超越0.8V门限(有50mV回差,即一旦跳过0.8V,然后只需不回落到0.75V以下,就依然起效果),1脚的软发动电容器就被芯片内部放电,作业频率添加以约束功率输出。在主电路短路的情况下,这一般使得电路的峰值电流简直稳定。考虑到过流时刻被2脚设置,假如电流持续增大,虽然频率添加,当电压超越另一比较器的基准电压(1.5V)时,驱动器将封闭,能量损耗简直回到发动之前的水平。检测信息被闭锁,只需当电源电压Vcc低于UVLO时,芯片才会被从头发动。假如这个功用不必,请将4脚接地。

7.LINE:输入电压检测。此端由分压电阻取样沟通或直流输入电压(在体系和PFC之间)进行维护。检测电压低于1.25V时,封闭输出(非闭锁)并开释软发动电容器。电压高于1.25V时从头软发动。这个比较用具有滞后效果:假如检测电压低于1.25V,内部的15uA恒流源被翻开。在7脚对地直接一只电容,以消除噪声搅扰。该脚电压被内部的6.3V齐纳二极管所限,6.3V齐纳二极管的导通使得芯片的输出关断(非闭锁)。假如该功用不被运用,该脚电压在1.25V到6V之间。

8.DIS:Disable,闭锁式驱动封闭。该脚内部衔接一只比较器,当该脚电压超越1.85V时,芯片闭锁式关机,只需当将芯片作业电压Vcc降低到UVLO门限之下时,才可以从头开端作业。假如不运用此功用,请将该引脚接地。

9.PFC_STOP:翻开PFC(功率因数校对)操控器的操控途径。这个引脚的敞开,是为了中止PFC操控器的作业,以到达维护意图或间歇作业形式。当芯片被DIS》1.85V、ISEN》1.5V、LINE》6V和STBY《1.25V封闭时,9脚输出被拉低。当DELAY端电压超越2V,且没有回复到0.3V之下时,该端也被拉低。在UVLO(低压闭锁)期间,该引脚是敞开的。答应此脚悬空不运用。

10.GND:芯片地。回路电流为低端门极驱动电流和芯片偏置作业电流之和。一切相关的地都应该和这个脚连通,而且要同脉冲操控回路分隔。

11.LVG:低端门极驱动输出。该脚可以供给0.3A的小驱动电流。源极0.8A(?)。吸入(?)峰值电流驱动半桥电路的低端MOS管。在UVLO期间,LVG被拉低到地电平。

12.Vcc:电源包含芯片的信号部分和低端MOS管的门极驱动。接一只小的滤波电容(0.1uF)有利于芯片信号电路得到一个洁净的偏置电压。

13.N.C.:空引脚,用于高电压阻隔,增大Vcc和14脚间的间隔。该针内部没有衔接,与高压阻隔,而且使得在PCB上可以满意安全规程(漏电间隔)的要求。

14.OUT:高端门极驱动的浮地。为高端门极驱动电流供给电流回来回路。应细心布局以防止呈现太大的低于地的毛刺。

15.HVG:高端悬浮门极驱动输出。该脚可以供给0.3A的小驱动电流。源极0.8A(?)。吸入(?)峰值电流驱动半桥电路的上端MOS管。有一只电阻经过芯片内部衔接到14脚(OUT)以保证在UVLO期间不悬浮驱动。

16.VBOOT:高端门极驱动起浮电源。在16脚(Vboot)与14脚(OUT)间衔接一只自举电容Cboot,被芯片内部的一个自举二极管与低端门极驱动器同步驱动。这个专利结构替换一般运用的外在二极管。