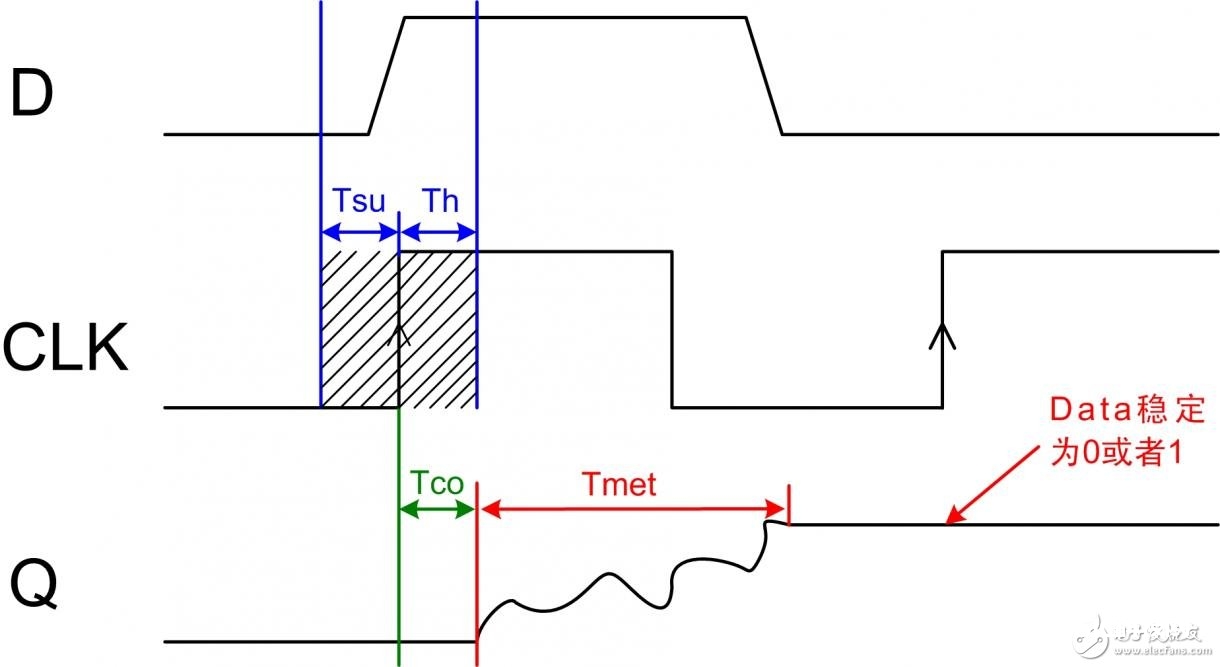

FPGA系统中三种方式减少亚稳态的产生-在FPGA系统中,如果数据传输中不满足触发器的Tsu和Th不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端在0和1之间处于振荡状态,而不是等于数据输入端D的值。

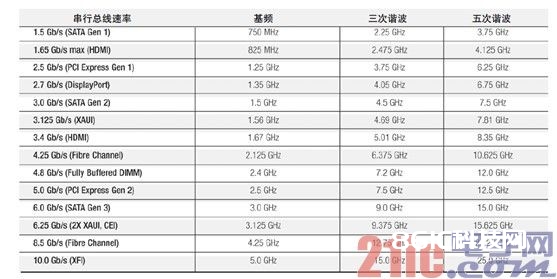

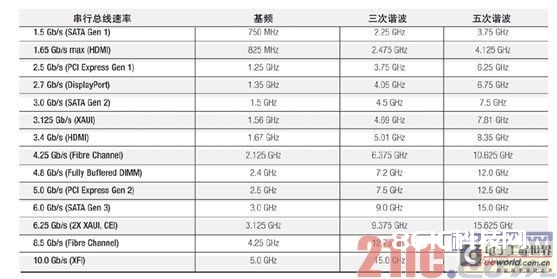

测量设备的特性可能会导致正常工作的DUT不满足一致性的要求。这个采集系统,包括探头、电缆、示波器,必须满足必须能让足够的信号能量被采集。下面列出好的采集系统关键因素:●带宽●足够的输入通道●采样率●样