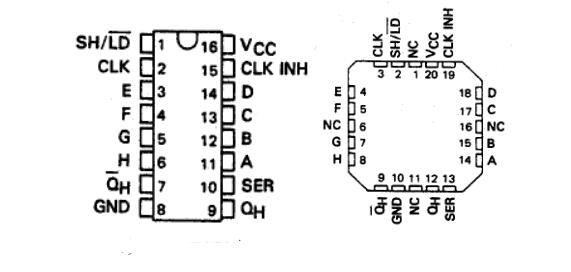

本站为您提供的74ls165中文资料汇总(74ls165引脚图及功能_工作原理及应用电路),本文详细介绍了74ls165中文资料,其中包括74ls165引脚图及功能、74ls165工作原理、真值表和时序图等工作参数和电气特性,另外还介绍了两款74ls165的应用电路图。

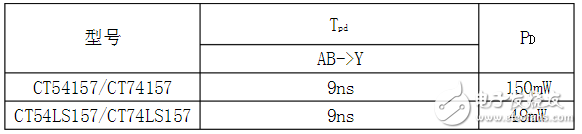

本站为您提供的74ls157中文资料汇总(74ls157引脚图及功能_逻辑图及特性参数),本文主要介绍了74ls157中文资料汇总(74ls157引脚图及功能_逻辑图及特性参数)。74ls157是四2选1数据选择器(有公共选通输入端),数据选择端(S)为四组共用,供四组从各自的2个数据(A1、B1、A2、B2、A3、B3、A4、B4)中分别选取1个所需数据,只有在四组共用的选通端G为低电平时才可选择数据。

本站为您提供的74ls266中文资料汇总(74ls266引脚图及功能_真值表及特性),本文主要介绍74ls266中文资料,首先介绍了74ls266引脚图及功能,其次介绍了74ls266真值表和极限值,最后阐述了74ls266的工作条件及特性,具体的跟随小编一起来了解一下。

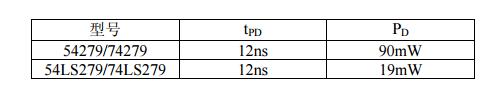

本站为您提供的74ls279中文资料汇总(74ls279引脚图及功能_逻辑图及特性),本文主要介绍74ls279中文资料,首先介绍了74ls27974ls279中文资料,其次介绍了74ls279逻辑图和真值表,最后阐述了74ls279极限值和特性,具体的跟随小编一起来了解一下吧。

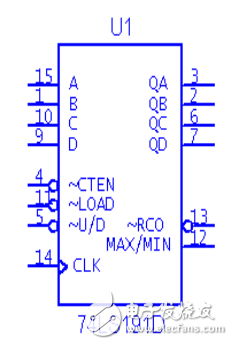

本站为您提供的74ls191中文资料汇总(74ls191引脚图及功能_逻辑功能及应用电路),本文主要介绍了74ls191中文资料汇总(74ls191引脚图及功能_逻辑功能及应用电路)。74LS191为可预置的四位二进制加/减法计数器,RCO进位/借位输出端,MAX/MIN进位/借位输出端,CTEN计数控制端,QA-QD计数输出端,U/D计数控制端,CLK时钟输入端,LOAD异步并行置入端(低电平有效)。

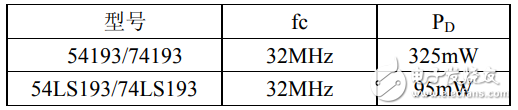

本站为您提供的74ls193中文资料汇总(74ls193引脚图及功能_工作原理及应用电路),本文主要介绍了74ls193中文资料汇总(74ls193引脚图及功能_工作原理及应用电路)。193的清除端是异步的。当清除端(CLEAR)为高电平时,不管时钟端(CDOWN、CUP)状态如何,即可完成清除功能。193的预置是异步的。当置入控制端(LOAD)为低电平时,不管时钟(CDOWN、CUP)的状态如何,输出端(QA-QD)即可预置成与数据输入端(A-D)相一致的状态。193的计数是同步的,靠CDOWN、CUP同时加在4个触发器上而实现。在CDOWN、CUP上升沿作用下QA-QD同时变化,从而消除了异步计数器中出现的计数尖峰。当进行加计数或减计数时可分别利用CDOWN或CUP,此时另一个时钟应为高电平。

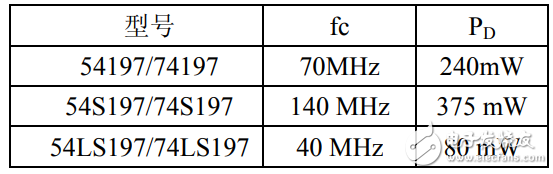

本站为您提供的74ls197中文资料汇总(74ls197引脚图及功能_逻辑功能及特性),本文主要介绍了74ls197中文资料汇总(74ls197引脚图及功能_逻辑功能及特性)。74ls197为可预置的二-八-十六进制计数器,异步清除端(CR)为低电平时,不管时钟端(CP0、CP1)状态如何,即可完成清除功能。计数/置入控制(CT/LD)为低电平时,不管时钟端(CP0、CP1)状态如何,即可完成预置功能。197还可作4位锁存器,此时CT/LD作为选通端。当CT/LD为低电平时,Q0~Q3随D0~D3而变化;当CT/LD为高电平时,只要时钟不作用,Q0~Q3将保持不变。

本站为您提供的74ls247中文资料汇总(74ls247引脚图及功能_工作原理及应用电路),本文主要介绍了74ls247中文资料汇总(74ls247引脚图及功能_工作原理及应用电路)。74ls247是4线——七段译码器/驱动器(BCD输入,OC,15V),输出端(a~g)为低电平有效,可直接驱动指示灯或共阳极LED。当要求输入0~15时,消隐输入(/BI)应为高电平或开路,对于输出0时还要求脉冲消隐输入(/RBI)为高电平或开路。