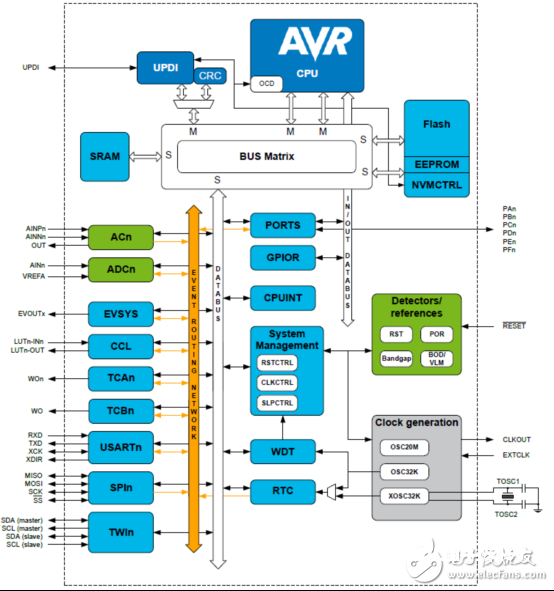

ATmega3208系列MCU物联网解决方案-Microchip公司的ATmega3208/3209/4808/4809是采用AVR处理器的megaAVR 0系列MCU,具有工作高达20MHz的硬件乘法器,以及高达48KB闪存储器,6KB SRAM和256B EEPROM,采用最新的技术和灵活的低功率架构,包括事件系统和SleepWalking,精密模拟特性和先进的外设,采用28,32或48引脚封装,主要用在工业,医疗,家庭自动化和物联网(IoT)应用.

基于EPF10K100EQ 240-132和Booth编码实现位浮点阵列乘法器的设计-随着计算机和信息技术的快速发展, 人们对微处理器的性能要求越来越高。乘法器完成一次乘法操作的周期基本上决定了微处理器的主频, 因此高性能的乘法器是现代微处理器中的重要部件。本文介绍了32 位浮点阵列乘法器的设计, 采用了改进的Booth 编码, 和Wallace树结构, 在减少部分积的同时, 使系统具有高速度, 低功耗的特点, 并且结构规则, 易于VLSI的实现。

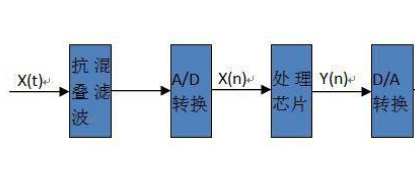

简析DSP的工作原理-DSP内部除了算术逻辑单元(ALU),还包括多个处理单元——辅助寄存器运算单元(ARAU),累加器(ACC),硬件乘法器(MULT),以及丰富的总线资源,它们的存在使得DSP可以拥有一些数字信号处理的特殊DSP指令,以及可以快速的访问存储以及并行操作的能力,保证数字信号处理中的实时的高速度、高精度累加即乘法等运算。

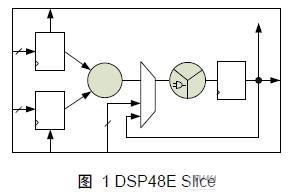

基于Adaboost算法结合Virtex5平台如何提升FPGA器件的性能-本文系统的实现主要用到了两类逻辑资源来优化系统性能:DSP48E Slice:25×18位二进制补码乘法器能产生48位全精度结果。此功能单元还能够实现诸多DSP模块如乘累加器、桶形移位器、宽总线多路复用器等。

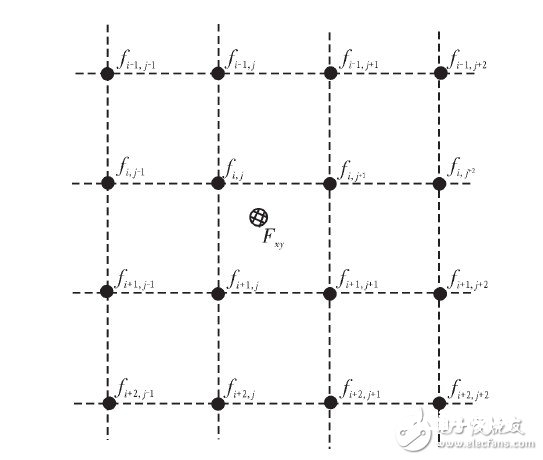

如何利用FPGA硬件实现固定倍率的图像缩放?-近年来,FPGA技术发展迅速,片内集成了PLL、硬件乘法器、存储器,具有了实现优秀算法的充足资源。许多航空电子嵌入式图像处理系统是由固定的视频源和显示设备组成,系统中图像缩放的倍率是固定的。文中针对此展开重点研究,基于FPGA硬件,实现固定倍率的图像缩放。