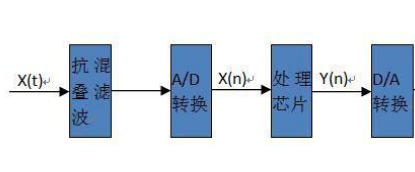

数字滤波器用于离散系统;模拟滤波器用于连续时间系统,也可以用在离散时间系统中,比如SC(开关电容)滤波器。数字滤波器由数字乘法器、加法器和延时单元组成的一种算法或装置。模拟滤波器有有源和无源的,有源滤

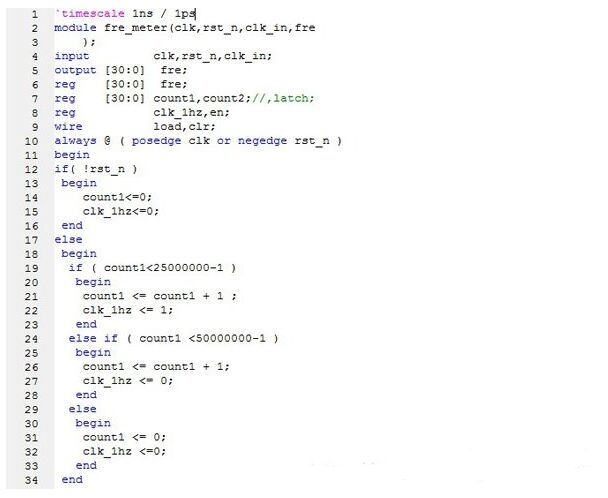

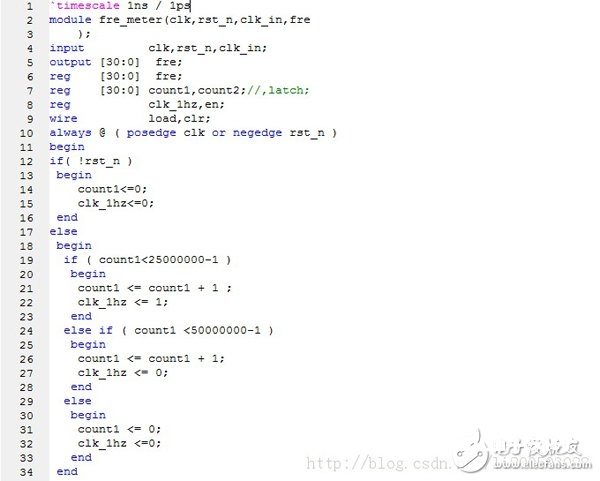

本设计充分利用了Vertex器件的LUTs(Look-Up Tables)替代触发器和基本门电路搭建乘法器和加法器这两个显著的结构特点,节省了大量的触发器资源,增加了器件利用率、布通率,DLL的运用降

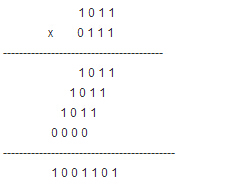

FPGA基于CORDIC算法的求平方实现-CORDIC是在没有专用乘法器(最小化门数量)情况下,一组完成特定功能的算法,包括平方、超越、Log、sin/cos/artan。原理为连续的旋转一个较小的角

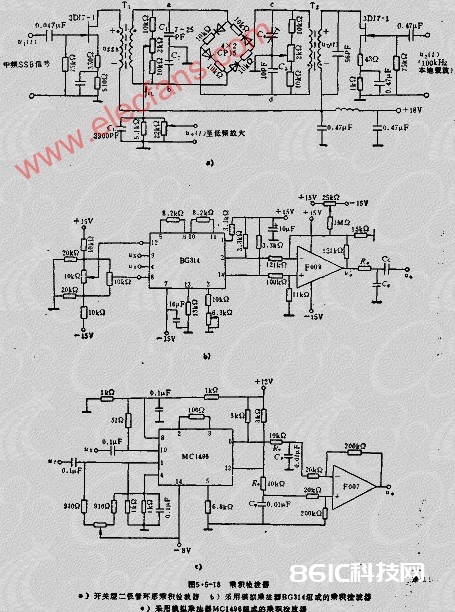

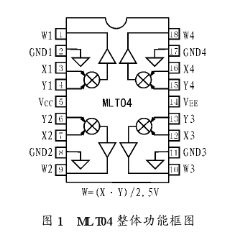

四通道四象限模拟乘法器MLT04的功能特点和应用电路分析-在高频电子线路中,振幅调制、同步检波、混频、倍频、鉴频等调制与解调的过程均可视为两个信号相乘的过程,而集成模拟乘法器正是实现两个模拟量电压或电流相乘的电子器件。采用集成模拟乘法器实现上述功能比用分立器件要简单得多,而且性能优越,因此集成模拟乘法器在无线通信、广播电视等方面应用较为广泛。