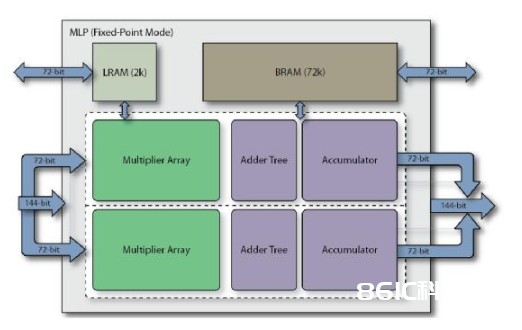

震惊!FPGA运算单元可支持高算力浮点-MLP全称Machine Learning Processing单元,是由一组至多32个乘法器的阵列,以及一个加法树、累加器、还有四舍五入rounding/饱和saturation/归一化normalize功能块。

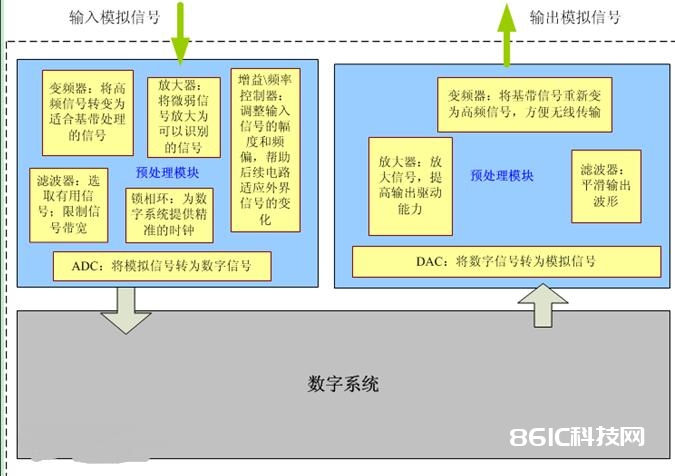

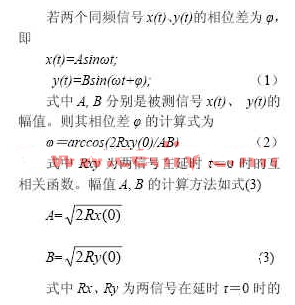

基于CPLD芯片EPF10K100TC144-3实现虚拟相位测量系统的应用方案-在图形化编程中,锁存器、乘法器、加法器和除法器均为LPM(参数化模块库) 中元件。在编程中可通过设置参数来实现器件运算速度和数据线宽度的配置。

基于Adaboost算法结合Virtex5平台如何提升FPGA器件的性能-本文系统的实现主要用到了两类逻辑资源来优化系统性能:DSP48E Slice:25×18位二进制补码乘法器能产生48位全精度结果。此功能单元还能够实现诸多DSP模块如乘累加器、桶形移位器、宽总线多路复用器等。