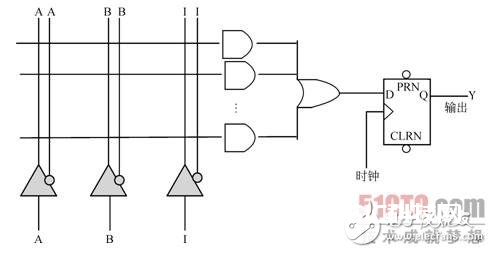

5大步骤完成FPGA的设计 可编程逻辑器件PAL介绍-将逻辑门和输出寄存器固定为通用逻辑后,选择使用逻辑输入及其互补逻辑,就可以建立任何逻辑功能。PAL主要由图1.5中的三部分构成,多次复制这三部分就可以形成复杂PAL器件。这里显示的可编程阵列是所选择的输入,将其连接到需要的与门。在输入和进入与门的线之间进行连接,可实现线与操作。与门输出构成乘积项。乘积项通过或门完成乘积和,从而产生最终函数输出。

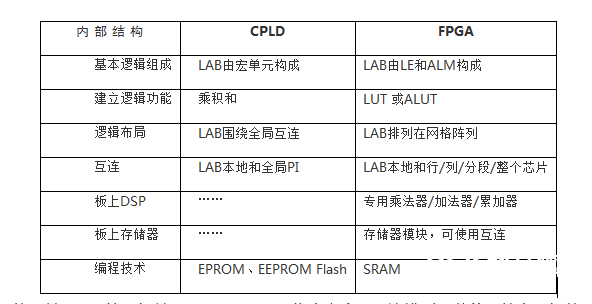

FPGA与CPLD的辨别和分类主要是根据其结构特点和工作原理。通常的分类方法是:将以乘积项结构方式构成逻辑行为的器件称为CPLD,如Lattice的ispLSI系列、Xilinx的XC9500系列、A

为什么不能将乘法器用作调制器或混频器?它们不是一回事吗?并非如此,了解它们之间的区别十分重要。乘法器有两个模拟输入,输出与两个输入幅度的乘积成比例。VOUT = K times; VIN1 times

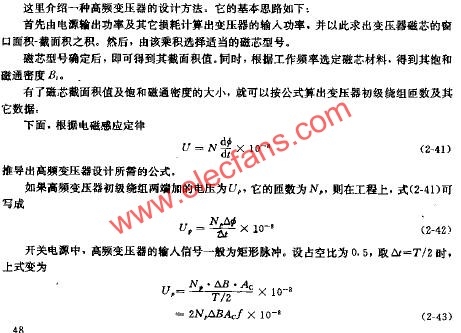

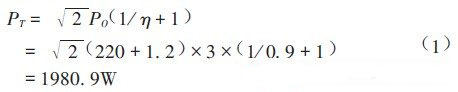

3开关变压器的设计采用面积乘积(AP)法进行设计。对于推挽逆变工作开关电源,原边供电电压UI=24V,副边为全桥整流电路,期望输出电压UO=220V,输出电流IO=3A,开关频率fs=25kHz,初定