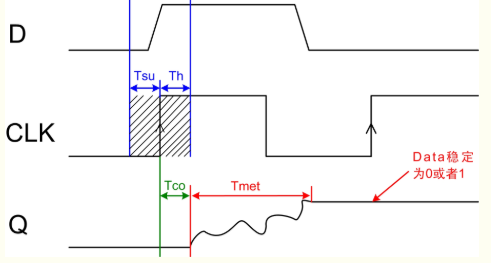

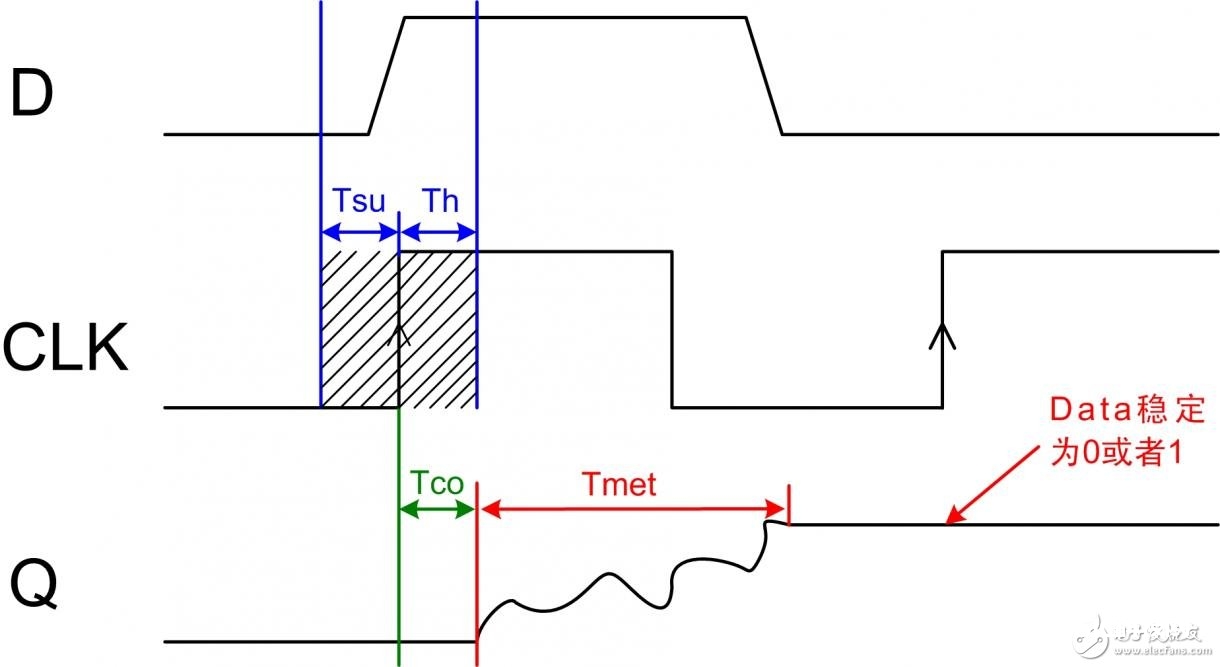

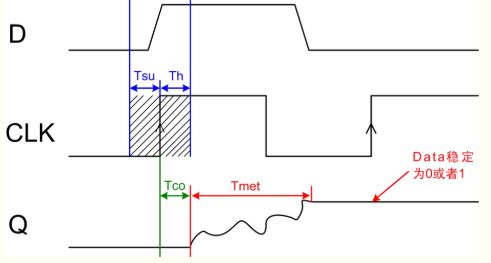

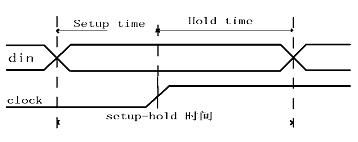

FPGA系统中三种方式减少亚稳态的产生-在FPGA系统中,如果数据传输中不满足触发器的Tsu和Th不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端在0和1之间处于振荡状态,而不是等于数据输入端D的值。

利用半拍错位同步法消除异步电路的亚稳态-当今的数字系统往往是围绕CPLD/ FPGA 进行设计的, 首选的方案是采用同步时序电路设计 , 也称作单时钟系统, 电路中所有触发器的时钟输入端共享同一个时钟, 每个触发器的状态变化都是在时钟的上升沿( 或下降沿) 完成的, 与时钟脉冲信号同步。

FPGA系统复位过程中的亚稳态原理-在复位电路中,由于复位信号是异步的,因此,有些设计采用同步复位电路进行复位,并且绝大多数资料对于同步复位电路都认为不会发生亚稳态,其实不然,同步电路也会发生亚稳态,只是几率小于异步复位电路。

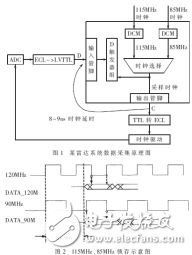

基于FPGA的自适应同步器电路设计详解- 在许多高速数据采集系统中,数据正确锁存是设计者必须要面对的问题。特别是在内部时钟与外部时钟采用同一个时钟源的基于FPGA的高速数据采集系统中,由于走线延时、器件延时、FPGA输入管脚延时,导致FPGA输入数据与FPGA内部时钟的相对相位关系不确定;在时钟频率可变的情况下,相对相位关系还会随频率变化。在FPGA内部一般采用D触发器实现对输入数据的采样。为了避免亚稳态 ,D触发器要求输入数据相对时钟沿满足一定的建立、保持时间,即输入数据与FPGA内部时钟要满足一定的相位关系。由于输入数据与采样时钟相对相位的不确定性,就有可能不满足FPGA内部D触发器的建立、保持时间,出现亚稳态。针对上述情况,本文给出在FPGA中可以自适应地选择时钟上升沿或下降沿采样的自适应同步器电路设计。该电路能够检测锁存时钟上升沿与输入数据

实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果对跨时钟域带来的亚稳态、采样丢失、潜在逻辑错误等等一系列问题处理不当,将导致系统无法运行。

利用半拍错位同步法消除异步电路的亚稳态-当今的数字系统往往是围绕CPLD/ FPGA 进行设计的, 首选的方案是采用同步时序电路设计 , 也称作单时钟系统, 电路中所有触发器的时钟输入端共享同一个时钟, 每个触发器的状态变化都是在时钟的上升沿( 或下降沿) 完成的, 与时钟脉冲信号同步。