HLS优化设计中pipeline以及unroll指令:细粒度并行优化的完美循环-HLS 优化设计的最关键指令有两个:一个是流水线 (pipeline) 指令,一个是数据流(dataflow) 指令。正确地使用好这两个指令能够增强算法地并行性,提升吞吐量,降低延迟但是需要遵循一定的代码风格。展开 (unroll) 指令是只针对 for 循环的展开指令,和流水线指令关系密切,所以我们放在一起首先我们来看一下这三个指令在 Xilinx 官方指南中的定义: Unroll: Unroll for-loops to create multiple instances of the loop body and its instructions that can then be scheduled independently. Pipel

当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些小技巧

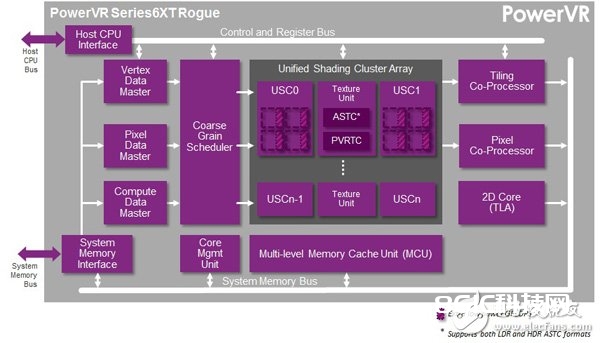

工程师分享:基于FPGA的GPU原型优化设计-Synopsys所做的第一步是启动一个概念验证项目。这个项目为Imagination的PowerVR Series6 GPU展示了基于FPGA的原型设计。

本站为您提供的MAX9030-MAX9034低成本单电源比较器,MAX9030/MAX9031/MAX9032/MAX9034单/双/四比较器专为采用+2.5V至+5.5V单电源供电的系统而优化设计,但也可工作于双电源下