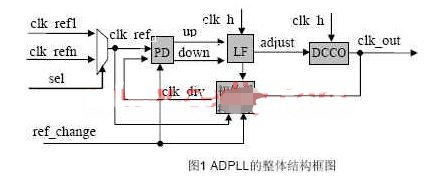

基于可编辑逻辑器件实现ADPLL的应用设计-随着数字电路技术的发展,特别FPGA技术的普遍应用,采用FPGA实现全数字锁相环(ADPLL)的应用越来越多。ADPLL设计简单、应用方便。本文介绍一种采用FPGA实现的ADPLL,该ADPLL用于产生SDH设备的外同步输出时钟。该锁相环具备传统的APLL的俘获时间短、有稳定的相差的优点,同时也具备DPLL的中心频点可编程调整、能够实现平滑源切换的优点。

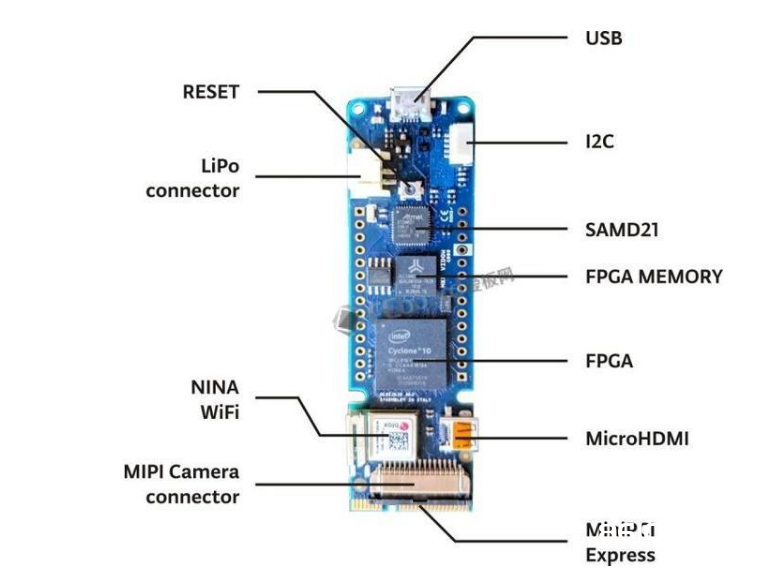

MKR Vidor 4000一款拇指型的FPGA开发板-MKR Vidor 4000作为一款拇指型的开发板,小巧精致是它固有的特性,这是优点,同时也是缺点。优点在于没有复杂的硬件,上手理解应该会比较简单;而缺点则是因为太过简单,所以注定不可能搭载很多功能,而且更多的功能实现都需要靠外接其它功能外设支持,成本花销会很大。

为应用选择最佳可编程SoC时进行的六个设计考虑-SoC FPGA器件在一个器件中同时集成了处理器和FPGA体系结构。将两种技术合并起来具有很多优点,包括更高的集成度、更低的功耗、更小的电路板面积,以及处理器和FPGA之间带宽更大的通信等等。这一同类最佳的器件发挥了处理器与FPGA系统融合的优势,同时还保留了独立处理器和FPGA方法的优点。