基于电路分割技术的查表法实现根升余弦脉冲成形滤波器FPGA设计-数字通信系统中,基带信号的频谱一般较宽,因此传递前需对信号进行成形处理,以改善其频谱特性,使得在消除码间干扰与达到最佳检测接收的前提下,提高信道的频带利用率。目前,数字系统中常使用的波形成形滤波器有平方根升余弦滤波器、高斯滤波器等。设计方法有卷积法或查表法,其中:卷积法的实现,需要消耗大量的乘法器与加法器,以构成具有一定延时的流水线结构。为降低硬件消耗,文献提出了一种分布式算法(Distributed Arithmetic,DA)的滤波器设计结构。它将传统的乘、累加运算转化为移位、累加运算,当运算数据的字宽较小时,极大地降低了硬件电路的复杂度,提高了响应速度;当运算数据的字长较长时,因其需要更多的移位迭代运算而不适合高速处理的需求。为此,文献提出了采用滤波器的多相结构与改进DA算法相结合的一种设

数控振荡器的基本原理及如何在FPGA中实现设计-本文介绍一种利用矢量旋转的CORDIC(COordination Rotation DIgital Computer)算法实现正交数字混频器中的数控振荡器(NCO)的方法。推导了CORDIC算法产生正余弦信号的实现过程,给出了在FPGA 中设计数控振荡器的顶层电路结构,并根据算法特点在设计中引入流水线结构设计。

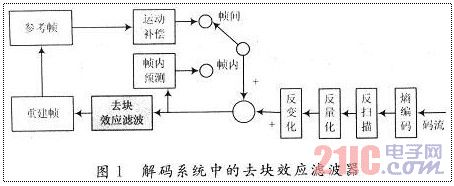

引 言图像的编解码技术是多媒体技术的关键,H.264/AVC是国际上最先进的视频压缩技术,其主要特点是采用小尺寸整数余弦变换、1/4像素的运动估计精度、多参考帧预测,基于上下文可变长度编码和环路内去块

介绍了塑料光纤数字基带传输系统中升余弦滚降FIR成形滤波器的设计原理,利用MATLAB确定滤波器系数,并按最小均方误差准则优化,分析讨论了该滤波器基于优化的分布式算法和Wallace加法器树的FPGA

本文首先介绍了查表算法和Cordic算法原理,在这两种算法基础上,用Verilog HDL语言对32位定点数的正余弦函数进行了编程设计,结合仿真综合结果,对这两种方法从运算精度,运算速度和占用硬件资源

为了满足陆上集群无线电(TETRA)数字集群系统对基带信号成形处理的要求,提出了一种用于TETRA数字集群系统的平方根升余弦(SRRC)滤波器设计,论述了基带成形滤波和SRRC滤波器的基本原理,分析了