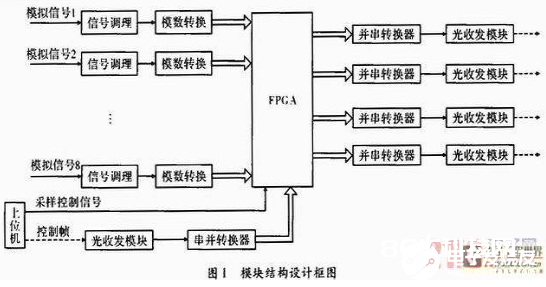

基于Cyclone系列FPGA和TMS320VC5416芯片实现多通道音频采集卡的设计-一个多通道数字音频系统必须考虑两个问题:采集到声音的质量问题和最终数字化后的音频存储的问题。由奈奎斯特定理知,如果要保证把采集到的音频信号完全无失真的恢复出来,采样率就必须至少是需采集音频信号频宽的2倍。由于现在大多数音频CODEC采用了Delta-Sigma Modulator,在保证采样率合适的情况下,声音质量一般是可以满足要求的。在船舶航行记录仪中,音频的频宽是150hz-6000hz,因此我们可以采用16khz的采样率和16位的量化位数。

基于System Verilog的可重用验证平台设计及验证结果分析-采用System Verilog语言设计了一种具有层次化结构的可重用验证平台,该平台能够产生各种随机、定向、错误测试向量,并提供功能覆盖率计算。将验证平台在Synopsys公司的VCS仿真工具上运行,并应用到包交换芯片的仿真验证中。仿真结果显示,新设计的验证平台能通过修改随机信号约束条件和产生随机信号的权重值,使芯片的功能覆盖率达到100%。

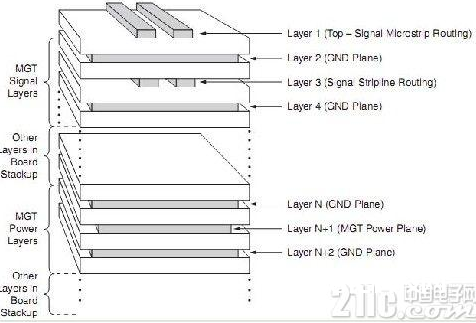

针对FPGA的GTP信号 PCB设计过程中需要考虑到以下因素-千兆位级串行I/O技术有着极其出色的优越性能,但这些优越的性能是需要条件来保证的,即优秀的信号完整性。例如,有个供应商报告说,他们第一次试图将高速、千兆位级串行设计用于某种特定应用时,失败率为90%。为了提高成功率,我们可能需要进行模拟仿真,并采用更复杂的新型旁路电路。

基于PLD器件EPM3256ATC144-10芯片实现固态功控系统的设计-如图1所示,每路SSPC取样电阻上的电压经过调理电路和低通滤波器以后,送到4通道A/D转换器的一个模拟输入端,A/D转换器的数据输出端、状态信号和控制信号分别接到CPLD的I/O引脚,便于程序控制A/D转换器的动作。CPLD另外的I/O口可以配置为MOSFET的开关命令输出口线、SSPC的状态输出口线和与上位机相连的控制命令输入口线;CPLD自身提供的JTAG BST电路,可以方便的测试系统内部器件之间的连接和检验器件的操作。

PLC连接编码器具体有哪些方式-西门子1200的数字输入开关点均提供了增量编码器脉冲信号的快速计数器功能,单相信号达到200KHz,双相信号(可四倍频及判断方向)达到80KHz,对于常用的2500PPR(每转分辨脉冲数),转速最快达到1920RPM(每分钟转数)。

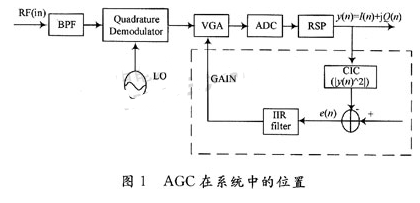

基于FPGA器件实现AGC算法和系统的设计-大多数接收机必须处理动态范围很大的信号,这需要进行增益调整,以防止过载或某级产生互调,调整解调器的工作以优化工作。在现代无线电接收装置中。可变增益放大器是电控的,并且当接收机中使用衰减器时,他们通常都是由可变电压控制的连续衰减器。控制应该是平滑的并且与输入的信号能量通常成对数关系(线性分贝)。在大多数情况下,由于衰落,AGC通常用来测量输入解调器的信号电平,并且通过反馈控制电路把信号电平控制在要求的范同内。

以FPGA为核心的高速数据采集控制模块设计流程概述-在雷达、通信、气象、军事监控及环境监测等领域,现场信号具有重要的作用。这些信号的主要特点是:实时性强、数据速率高、数据量大、处理复杂。为能够完整、准确地捕获到各种信号并及时进行处理,需要临测系统能够具备任意长度连续采集和存储的功能,且具有较高的数据传输率。考虑到FPGA拥有丰富的可编程I/O引脚、时钟频率高、时序控制精确、运行速度快、编程配置灵活等特点,采用其作为核心控制模块。因为光纤通信使用简单的点到点互连,具有传输损耗低、传输频带宽、速率高和抗电磁干扰等优点,在增加可靠性的同时降低了电缆连接的复杂程度,所以采用光纤作为信号传输媒介。

SoPC与CORDIC算法相结合的通用调制解调器设计方案-软件无线电要求在通用硬件平台上通过运行不同软件实现多种调制解调方式,这就要求为信号的调制及解调建立通用模型。当代无线通信中,理论上各种通信信号都可采用正交调制方法加以实现,所以,采用正交调制可以建立统一的模型,适用于软件无线电实现。

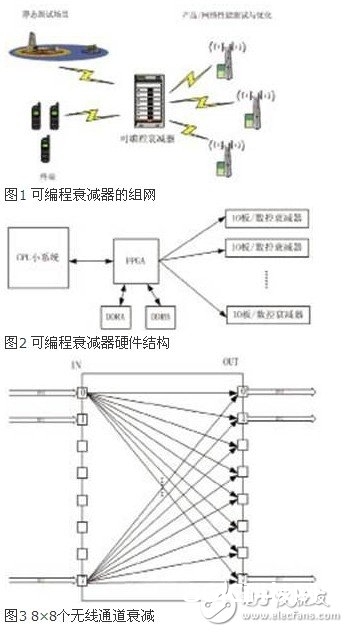

这种可编程衰减器最高可支持8×8输入输出的矩阵结构-可编程衰减器位于基站和终端之间,通过对射频信号的衰减控制,实现对无线信号的模拟,从而实现对测试场景的模拟。可编程衰减器提供多个数控接口,从小到大可以构建各个层次的测试网络。所构成的衰减矩阵通过模拟空口信道实现移动、切换、覆盖等多种测试项。

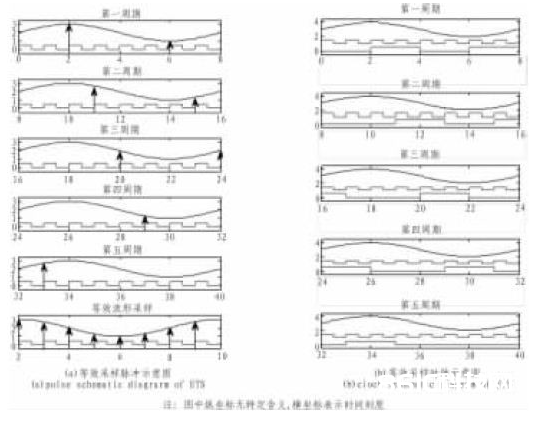

基于FPGA采样技术的等效时间采样原理剖析-在现代电子测量、通讯系统以及生物医学等领域,经常涉及对宽带模拟信号进行数据采集和存储,以便计算机进一步进行数据处理。为了对高速模拟信号进行不失真采集,根据奈奎斯特定理, 采样频率必须为信号频率的2 倍以上,但在电阻抗多频及参数成像技术中正交序列数字解调法的抗噪性能对信号每周期的采样点数决定,采样点数越多,抗噪性能越高。当采样信号频率很高时,为了在被采样信号的一周期内多采样,就需要提高采样时钟的频率,但是由于系统的ADC 器件时钟速率并不能达到要求的高频速率或者存储处理速度等不能满足要求因此我们可以采用低速ADC 器件通过等效时间采样来对宽带模拟信号进行数据采集从而使系统易于实现。