如何使用C51单片机中的位域功能-typedef struct

{

uchar DC0_ALA:1; //电源0告警

uchar DC1_ALA:1; //电源1告警

uchar AC_ALA:1; //停电告警

uchar UN_H_ALA:1; //同频信道机失锁告警

uchar UN_L_ALA:1; //异频信道机失锁告警

uchar FAR_ALA:1; //远端通讯故障告警

uchar OPEN_ALA:1; //门襟告警

uchar x:1;

基于XCV200/300PQFP240和TMS320C40实现背板开发设计-在移动通信和高速无线数据通信中,多径效应和信道带宽的有限性以及信道特性的不完善性导致数据传输时不可避免的产生码间干扰,成为影响通信质量的主要因素,而信道的均衡技术可以消除码间干扰和噪声,并减少误码率。其中判决反馈均衡器(DFE)是一种非常有效且应用广泛得对付多径干扰得措施。目前DFE大致有以下几种实现方法:

基于FPGA芯片XC3S2000实现卫星信道模拟器的设计-1.信道的选取:电波经过反射、折射、散射等多条路径传播到达接收机后, 总信号的强度服从瑞利分布。同时由于接收机的移动及其他原因,信号强度和相位等特性又在起伏变化,故称为瑞利衰落。但是对于卫星系统,收到的信号中除了经反射折射散射等来的信号外,还有从卫星直接到达地面接收机的信号,那么总信号的强度服从莱斯分布,故称为莱斯(Rice)衰落;另外,一般认为卫星信道中的噪声是加性高斯白噪声(AWGN)。所以模型中的信道选用Rice衰落信道和AWGN信道。

基于Cyclone系列FPGA器件和UART功能实现误码率测试仪器的设计-在通信系统的设计实现过程中,都需要测试系统的误码性能。而常见的误码率测试仪多数专用于测试各种标准高速信道,不便于测试实际应用中大量的专用信道,并且价格昂贵,搭建测试平台复杂。随着大规模集成电路的迅速发展,FPGA在保持其集成度高,体积小,功耗低,性价比高特性的同时,能够实现越来越复杂设计功能,日益广泛的应用于通信设备的设计实现。

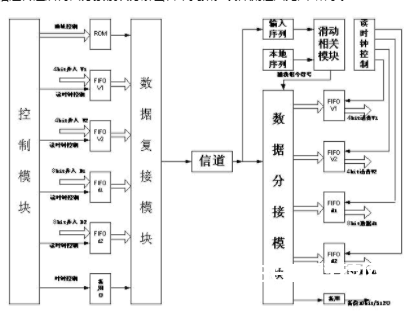

基于VIRTEX-ⅡPRO系列FPGA实现多业务双向通信系统的设计-随着现代通信向着多业务方向发展,为了节省信道资源、降低调制解调设备的复杂度,数据复接设备得到了更充分的利用。它能将多路不同类型的数据流复接成一路高速数据流,通过信道传输,在收端分接出发端对应的数据流,以实现多业务双向通信。

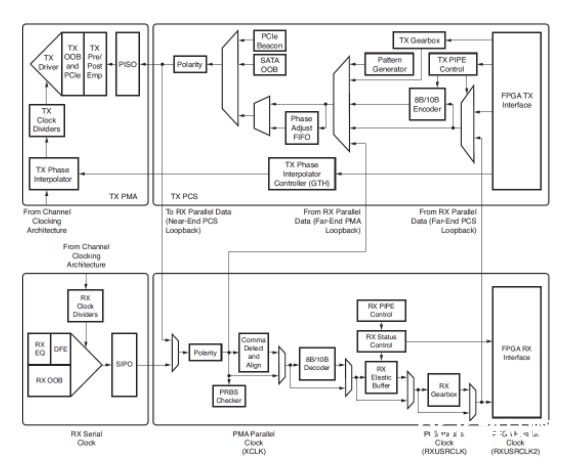

Kintex7的SERDES的结构图 CPRI应用的应用-Kintex7系列的GTX,以其良好的性能和功耗表现,已经成为业界FPGA选型时的明星。由于其良好的DFE性能,它能提供高达12.5Gbps的过背板能力,能支持在插损高达30dB的信道上可靠传输。在众多的SERDES应用中,有些应用比较特别,那就是需要在实际运行过程中动态切换GTX的链路速率,如无线中的CRPI接口,需要同时支持9.8G,4.9G,2.4G等众多速率。

低密度校验 (LDPC) 迭代解码读取信道使 2.5 英寸驱动器单磁盘容量高达 500GB,3.5 英寸驱动器单磁盘容量则高达 1TB2011 年 7 月 13 日,北京 讯 – LSI 公司(NYS