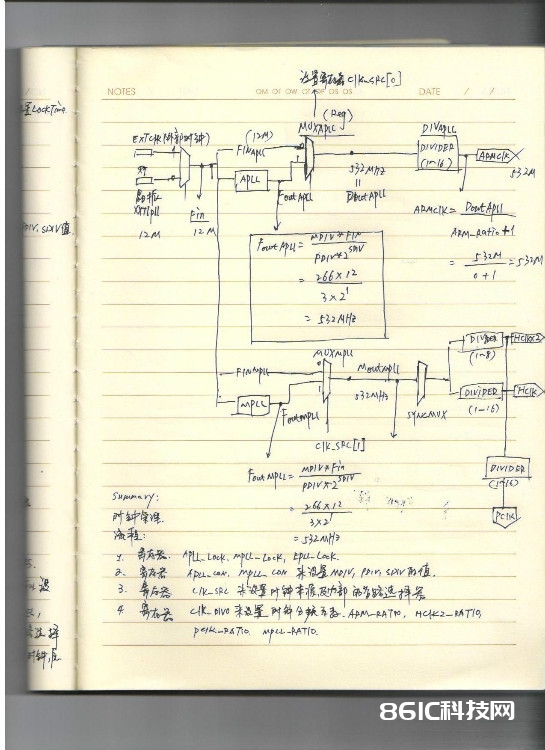

STM32的各种时钟系统的应用解析-在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

①、HSI是高速内部时钟,RC振荡器,频率为8MHz。

②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

③、LSI是低速内部时钟,RC振荡器,频率为40kHz。

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

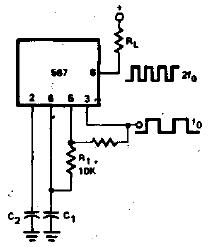

⑤、PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

如何使用STM32单片机设置PWM输出-环境:

主机:XP

开发环境:MDK4.23

MCU:STM32F103CBT6

说明:

使用内部8M晶振,倍频到64M供给TIM3定时器,PA6(通道1)上产生640K,50%方波

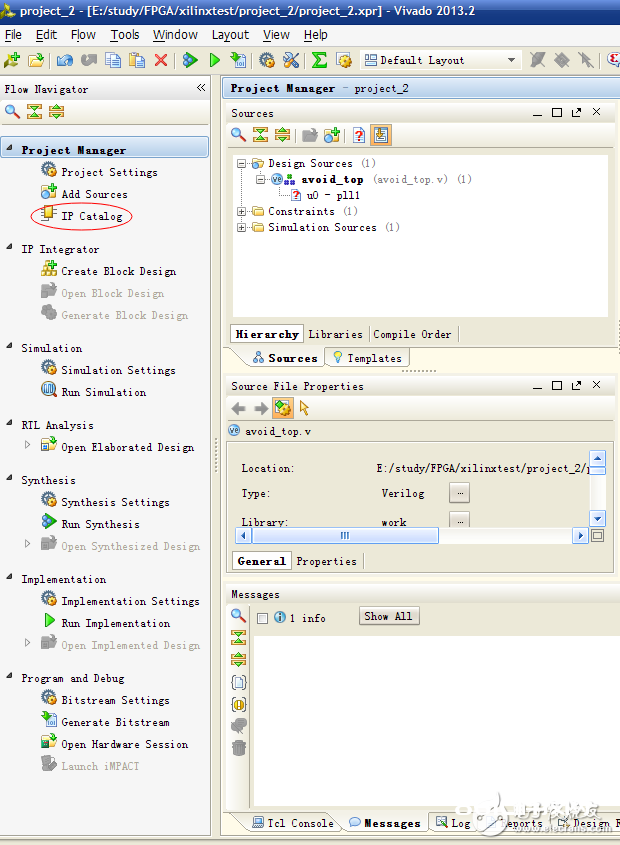

Vivado中PLL开发调用IP的方法-在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,这是同步时序电路的关键,这时就需要使用到时钟向导IP,下面就介绍一下在vivado中进行PL开发时调用IP的方法。

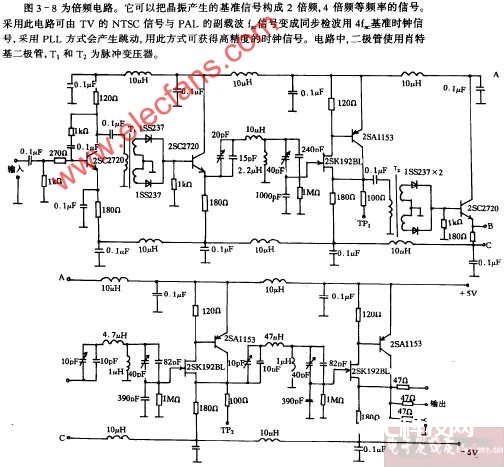

一种全新的以FPGA为基础的全新锁相倍频系统方案设计-随着数字时代的到来,越来越多的领域采用集成电路来设计电路,FPGA/CPLD等EDA设计更为广大硬件工程师所接受。其模块化设计为设计人员带来了很多方便,节约了系统的开发时间,使设计人员只需要调用这些模块或者IP核,然后组合起来就可以实现一个简单的功能。全数字锁相环(DPLL)就是其中一个典型的例子。然而DPLL在应用时存在很多缺陷,例如锁相时间长、捕捉带窄等。为了避免这些缺点,本文设计了一种全新的相位跟踪倍频系统,有效地改善了DPLL的这些指标,并在项目中得到了良好的应用。

调用Vivado IP核的方法-在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

摘要:根据BPSK调制信号调制机理和平方倍频法原理,在FPGA平台上设计实现了BPSK调制信号载波频率估计单元。利用ModelSim仿真环境对载频估计功能进行仿真,验证了平方倍频法对BPSK信号进行载