新建STM32工程全局声明两个宏的原因-在uVision中新建STM32工程后,需要从STM32标准库中拷贝标准外设驱动到自己的工程目录中,此时需要在工程设置->C/C++选项卡下的Define文本框中键入这两个全局宏定义。

以Spartan3系列为例 详解FPGA DCM-FPGA看上去就是一个四方形。最边缘是IO Pad了。除去IO Pad,内部还是一个四方形。四个角上各趴着一个DCM。上边缘和下边缘中间则各趴着一个全局Buffer的MUX。这样的好处是四个DCM的输出可以直接连接到全局Buffer的入口。

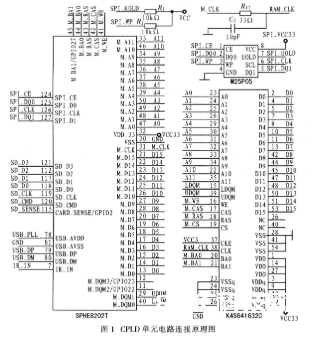

基于XC2C128-7V0100 CPLD器件实现低功耗信号发射电路的设计-Xilinx公司推出的CoolRunner-II系列中的XC2C128-7V0100。该器件采用第二代快速零功率(FZP)技术,以便在尽可能低的功耗情况下提供最佳的性能,如:采用1.8 V的内核电压,可提供300 MHz的性能,且耗功小于100μA。另外,该器件还具有体积小,价格低和稳定度高等优点,符合信号发射系统要求。XC2C128包含了16个内部互联功能块(AIM),每个AIM能为功能块提供40个输入,每个功能块包含16个宏单元,这些宏单元同时包含大量的配置寄存器。另外,这些寄存器能被全局预置和复位,也可被提前设置成D或T触发器,有多种时钟信号,分别为全局或部由路服务。例如在同步时。可同时应用3个不同的时钟信号。

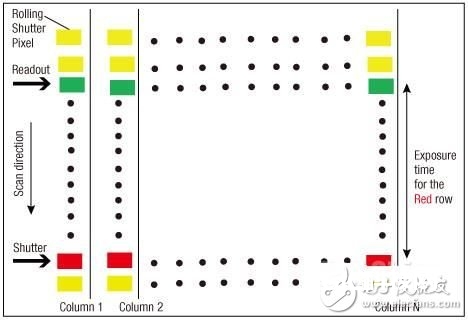

全局快门像素技术在CMOS图像传感器上的应用-传统上,全局快门像素技术主要用于CCD图像传感器。由于CMOS图像传感器的不断普及,且由于机器视觉、电影制作、工业、汽车和扫描应用要求必须以高图像品质捕捉快速移动的物体,图像传感器供应商Aptina公司已经致力于克服在CMOS图像传感器上使用全局快门像素技术的相关传统障碍。

FPGA全局时钟资源相关Xilinx器件原语及使用,FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB

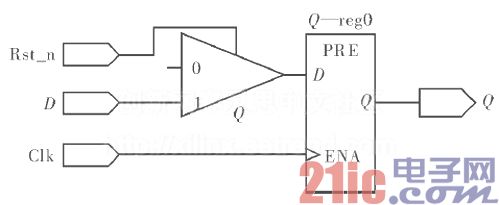

对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局异步