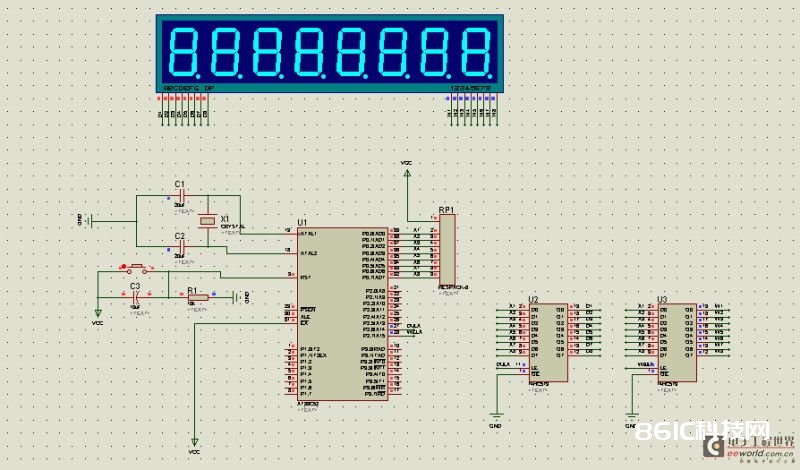

全局图:放大图:CODE:includereg52h>sbitdula=P2^6;sbitwela=P2^7;voidmain(){wela=1;P0=0x00;wela=0;dula=1;P0

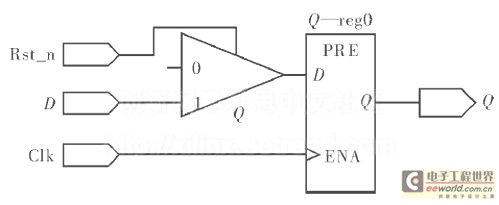

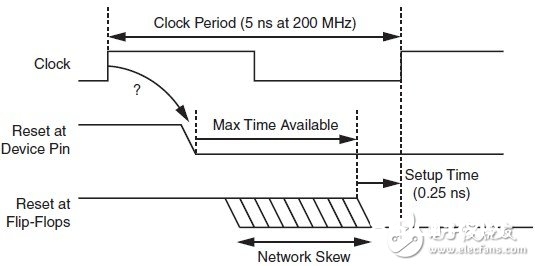

对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局异步

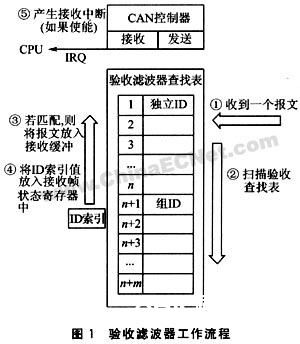

Philips公司的LPC2000系列32位ARM微控制器为内嵌的CAN控制器提供了全局的标识符查询功能,能实现复杂的报文ID过滤,而且可以大大减轻微控制器的负担。本文介绍了LPC2000系列ARM微

FPGA全局时钟和第二全局时钟资源的使用方法-目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般

在FPGA开发中尽量避免全局复位的使用?(2)-在Xilinx 的FPGA器件中,全局的复位/置位信号(Global Set/Reset (GSR))(可以通过全局复位管脚引入)是几乎绝对可靠的,因为