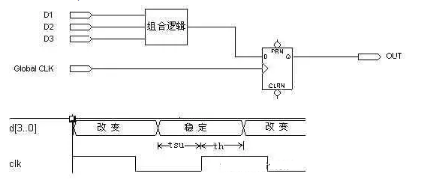

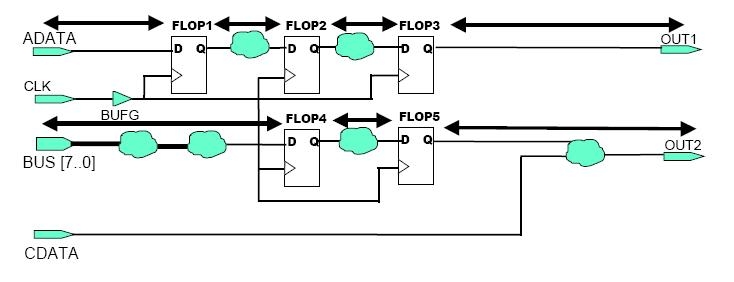

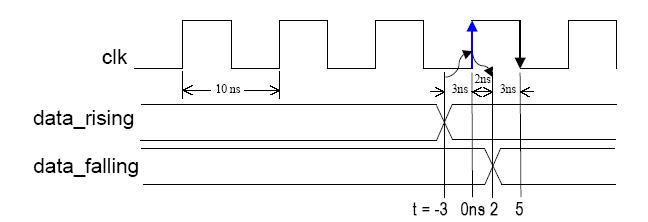

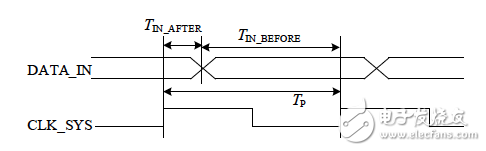

FPGA实战开发技巧(5)-一般来讲,添加约束的原则为先附加全局约束,再补充局部约束,而且局部约束比较宽松。其目的是在可能的地方尽量放松约束,提高布线成功概率,减少ISE 布局布线时间。典型的全局约束

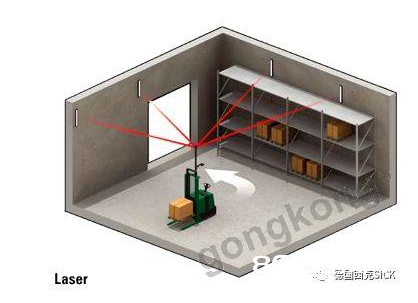

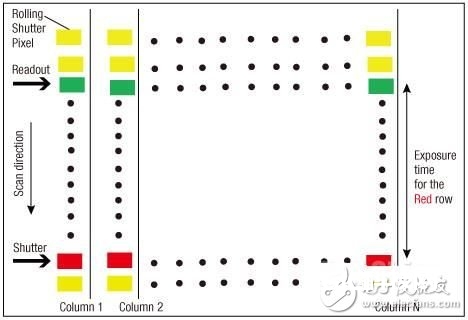

全局快门像素技术在CMOS图像传感器上的应用-传统上,全局快门像素技术主要用于CCD图像传感器。由于CMOS图像传感器的不断普及,且由于机器视觉、电影制作、工业、汽车和扫描应用要求必须以高图像品质捕捉快速移动的物体,图像传感器供应商Aptina公司已经致力于克服在CMOS图像传感器上使用全局快门像素技术的相关传统障碍。

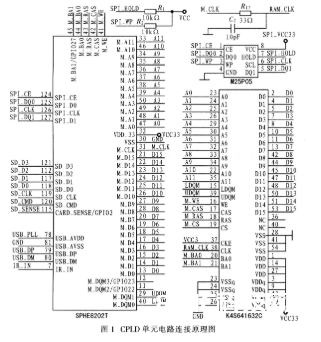

基于XC2C128-7V0100 CPLD器件实现低功耗信号发射电路的设计-Xilinx公司推出的CoolRunner-II系列中的XC2C128-7V0100。该器件采用第二代快速零功率(FZP)技术,以便在尽可能低的功耗情况下提供最佳的性能,如:采用1.8 V的内核电压,可提供300 MHz的性能,且耗功小于100μA。另外,该器件还具有体积小,价格低和稳定度高等优点,符合信号发射系统要求。XC2C128包含了16个内部互联功能块(AIM),每个AIM能为功能块提供40个输入,每个功能块包含16个宏单元,这些宏单元同时包含大量的配置寄存器。另外,这些寄存器能被全局预置和复位,也可被提前设置成D或T触发器,有多种时钟信号,分别为全局或部由路服务。例如在同步时。可同时应用3个不同的时钟信号。