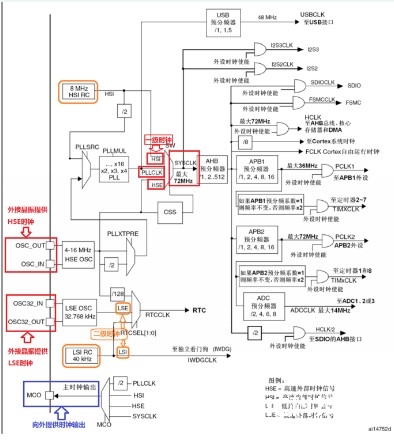

基于STM32时钟系统的开发及配置-研究过时钟来源,再来研究时钟的去向,MCU自身要能正常运作,即需要一个时钟,这个时钟既是系统时钟(SYSCLK),而基本上所有外设的时钟均来自于这个系统时钟(SYSCLk)。然后由系统时钟对外提供各种外设时钟。

FPGA设计中的异步复位同步释放问题-异步复位同步释放 首先要说一下同步复位与异步复位的区别。 同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。异步复位的好处是速度快。 再来谈一下为什么FPGA设计中要用异步复位同步释放。

今天写总结再来分析一下s3c2410_nand_calc_rate函数,终于知道问题在哪了,之前的打印内容如下:plat->tacls:0plat->twrph0:3plat->tw