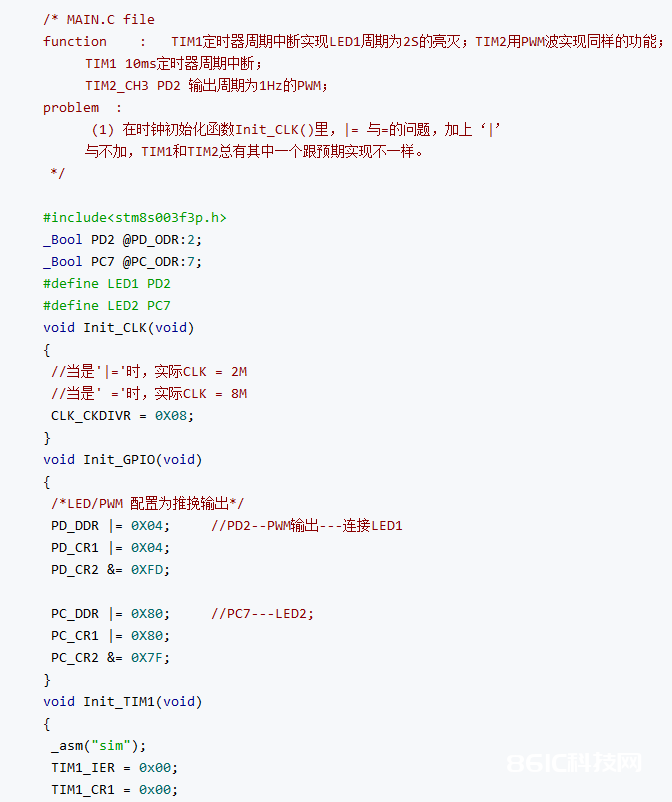

STM8S的定时器周期中断时钟测试系统-因为STM8S默认使用内部16M高速RC振荡器,且8分频,则系统启动主时钟为2M。即CLK_CKDIVR = 0X18;,如果再去赋值CLK_CKDIVR |= 0X08; 则主时钟还是不变即0X18,但是如果赋值为CLK_CKDIVR = 0X08;,则主时钟就会改变,变为8M。

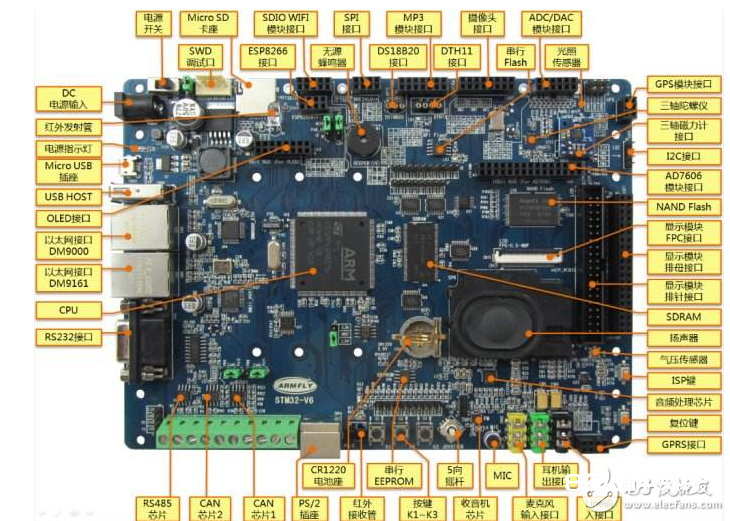

基于STM32内置ADC实现简易示波器的程序设计与实现-ADC转换:STM32增强型芯片内置的2个独立ADC,可以有16个通道,并且2个通道可以并行的同步采样,触发方式很灵活,可以通过TIMER以及外部电平等方式触发,并行方式下ADC2自动同步于ADC1;ADC在最高速采样的时候需要1.5+12.5个ADC周期,在14M的ADC时钟下达到 1Msps的速度,因为我主频是72M所以4分频后稍微高了点,18MHZ的ADC时钟,采样速度应该高于1M了。ADC 采样2路同时采样方式,用TIM2 CC2来生成时钟信号触发ADC来实现指定频率的采样。

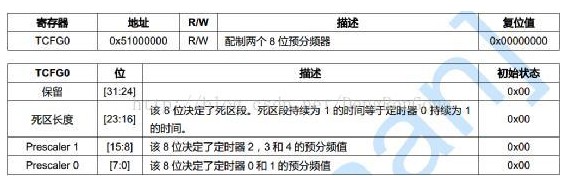

基于S3C2440A定时器的正确使用方法-定时器0和1共用一个8位预分频器,定时器2、3和4共用另外的8位预分频器。每个定时器都有一个可以生成5种不同分频信号(1/2,1/4,1/8,1/16和TCLK)的时钟分频器。每个定时器模块从相应8位预分频器得到时钟的时钟分频器中得到其自己的时钟信号。8位预分频器是可编程的,并且按存储在TCFG0和TCFG1寄存器中的加载值来分频PCLK

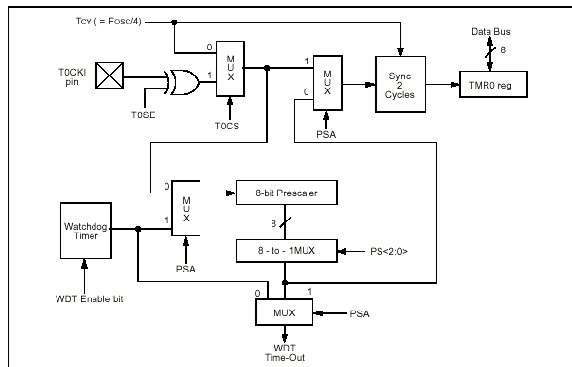

PIC单片机中预分频器的作用-1、从RTCC到WDT的改变 MOVLW B‘XX0X0XXX’ ;选择内部时钟和新的预分频值

OPTION ;如果新的预分频值=“000”或者

CLRF RTCC ;=“001”,则暂时先选一个另外的值

MOVLW B‘XXXX1XXX’ ;清零RTCC和预分频器

OPTION ;选择WDT为对象,但不要改变预分频值

CLRWDT ;清WDT和预分频器

MOVLW B‘XXXX1XXX’ ;选择新的预分频值

基于lpc1768的系统时钟设计-//PLL0时钟配置

LPC_SC-》SCS=0X00000020; /*使能外部主晶振,频率范围1-20M*/

if(LPC_SC-》SCS&(1《《5)) /* 主时钟被使能 */

{

while((LPC_SC-》SCS&(1《《6))==0);/* 等待主晶振使能并稳定 */

}

LPC_SC-》CCLKCFG=0x00000003; /* 选择PLL到CCLK的分频 4 */

LPC_SC-》PCLKSEL0=0x00000000; /*选择外设时钟从CCLK的分屏 均为0,均为4分频率,后期可改 */

LPC_SC-》PCLKSEL1=0x00000000;

基于STM8SF103定时器的使用方法解析-这个定时器的时钟源是系统时钟源(fMaster),然后直接通过预分频器分频后供CK_CNT使用。如:系统频率为4MHz,经过128分频后,提供给定时器使用的频率就为 31250Hz

因为项目需要,我这里使用的内部RC 16MHz振荡器,并进行LSI 4分频,所以主频为4MHz。