基于可编程逻辑芯片和CPU实现数字锁相环频率合成器的设计-数字锁相环频率合成系统的工作原理是:锁相环对高稳定度的基准频率(通常由晶体振荡器直接或经分频后提供)进行精确锁定,环内串接可编程的分频器,通过编程改变分频器的分频比,使环路总的分频比为N(可通过编程改变),从而环路稳定的输出 N倍的基准频率,而整个程序和系统的控制是要由CPU来完成的。

基于复杂可编程逻辑器件和VHDL语言实现半整数分频器的设计-在数字系统设计中,根据不同的设计需要,经常会遇到偶数分频、奇数分频、半整数分频等,有的还要求等占空比。在基于cpld(复杂可编程逻辑器件)的数字系统设计中,很容易实现由计数器或其级联构成各种形式的偶数分频及非等占空比的奇数分频,但对等占空比的奇数分频及半整数分频的实现较为困难。

本站为您提供的74ls390中文资料汇总(74ls390引脚图及逻辑功能_工作原理及特性),本文主要介绍了74ls390中文资料汇总(74ls390引脚图及逻辑功能_工作原理及特性)。74ls390是LSTTL型双四位十进制计数器。这种双单片电路有八个主从触发器和附加门,以构成两个独立的4位计数器,可以实现等于2分频、5分频乃至100分频的任何累加倍数的周期长度。当连成二—五进制计数器时,可以用独立的2分频电路在最后输出级形成对称波形(矩形波)。每个计数器又有一个清除输入和一个时钟输入。由于每个计数级都有并行输出,所以系统定时信号可以获得输入计数频率的任何因子。

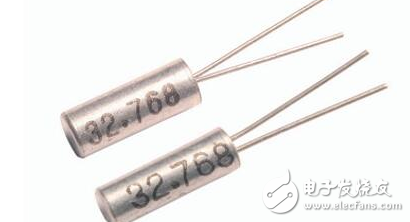

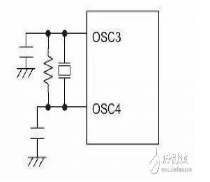

本站为您提供的对32.768KHz晶振的极致研究、专业应用,32.768KHz是一个标准的频率, 32.768KHz的时钟晶振产生的振荡信号经过石英钟内部分频器进行15次分频后得到1Hz秒信号,即秒针每秒钟走一下,石英钟内部分频器只能进行15 次分频,要是换成别的频率的晶振,15次分频后就不是1Hz的秒信号,时钟就不准了。

本站为您提供的32.768KHZ晶振的含义与发展,32.768KHZ是一个很有意义的数字,我们每天都要用到它,它给我们带来太多的好处。只是生活中太少有人去关注了,只关注着它给我们带来的演变数字。32.768khz比较容易分频以便于产生1秒的时钟频率,因为32768等于2的15次方。

本站为您提供的32768晶振实现秒信号,本文主要介绍了32768晶振实现秒信号。32.768KHZ的时钟晶振产生的振荡信号经过石英钟内部分频器进行15次分频后得到1HZ秒信号,即秒针每秒钟走一下,石英钟内部分频器只能进行15 次分频,要是换成别的频率的晶振,15次分频后就不是1HZ的秒信号,时钟就不准了。32.768K=32768=2的15次方,数据转换比较方便、精确。