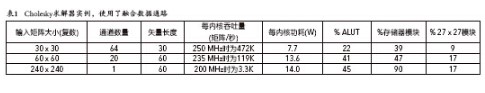

Altera FPGA硬核浮点DSP模块解决方案提高运算性能-以往FPGA在进行浮点运算时,为符合IEEE 754标准,每次运算都需要去归一化和归一化步骤,导致了极大的性能瓶颈。因为这些归一化和去归一化步骤一般通过FPGA中的大规模桶形移位寄存器实现,需要大量的逻辑和布线资源。通常一个单精度浮点加法器需要500个查找表(LUT),单精度浮点要占用30%的LUT,指数和自然对数等更复杂的数学函数需要大约1000个LUT。因此随着DSP算法越来越复杂,FPGA性能会明显劣化,对占用80%~90%逻辑资源的FPGA会造成严重的布线拥塞,阻碍FPGA的快速互联,最终会影响时序收敛。

初值预置电路考虑到控制信号与输入变量的关系,需要用一个数据选择端,同时由于数据是由四位二进制数所组成,所以共选用两个双4选1数据选择器74153。74153的输出受与4516相连的加法器74390的输

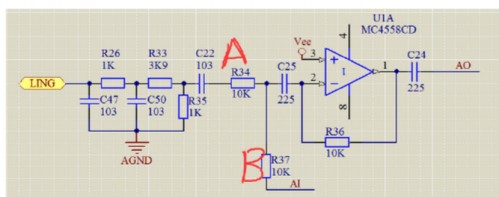

MAX11503是带有Y/C加法器和色度信号禁止的低功耗视频放大器。该器件接受S端子输入或Y/C信号,与亮度(Y)、色度(C)信号叠加产生复合CVBS信号,可以直接与TV显示器连接。MAX11503能