单片机C语言中变量的定义方法解析-#pragma rambank0 ;即以关键词#pragma开始,rambank0指明资料区块为第0块。

unsigned char m_acc; ;定义一个无符号字符型变量m_acc。

unsigned char m_ststus; ;定义一个无符号字符型变量m_status。

#pragma norambank ;norambank关键词表示变量在数据区块0的定义结束。

超低功耗iCE40 HX系列架构图分析-lattice公司的iCE40 HX超低功耗mobileFPGA系列,和其它任何的CPLD或FPGA器件相比,可提供最低的静态和动态功耗,大约640到7680个逻辑单元和触发器,每个器件包含8到32个RAM区块,每个区块有4Kb存储,用于数据存储和缓冲,特别适合对成本敏感和量大的应用.本文介绍了iCE40 HX系列主要特性,iCE40 HX系列架构图,主要产品和特性,以及iCEblink40 iCE40HX1K 评估板主要特性,电路图,主要元件清单和PCB元件布局图. The Lattice Semiconductor iCE40 LP-Series and HX-Series programmable logic family are designed

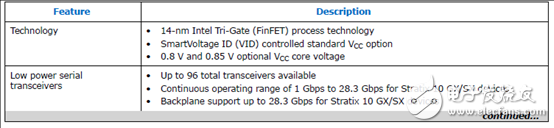

Stratix 10 SoC FPGA器件案例(应用、特性、电路图)-Intel公司的Stratix 10 SoC FPGA系列采用14nm三栅极(FinFET)和异构三维封装系统工艺技术,比以前高性能SoC FPGA提供2x核性能和节省多达70%的功耗, 单片核架构多达550万个逻辑单源(LE),多达96个全双工收发器通路,收发器数据速率高达28.3Gbps,嵌入eSRAM (45 Mbit)和M20K (20 kbit)SRAM存储器区块,基于PLL的分数合成和超低抖动LC振荡器,硬PCI Express Gen3 x16 IP区块,每个收发器通路中有硬10GBASE-KR/40GBASE-KR4 FEC,每个引脚的硬存储器控制器和PHY支持DDR4速率高达2666Mbps,以及硬定点和IEEE 754兼容

VR产业的生态圈涵盖了三大主要平台:主件、配件及素材平台。阐述了这三大平台之间的密切关系,然后说明了如何设计“去中心化”VR素材平台,结合区块链技术来保护VR素材IP,推广有互信的IP交易,大幅促进V

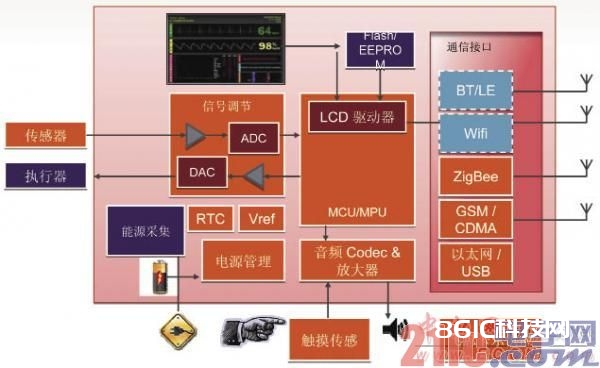

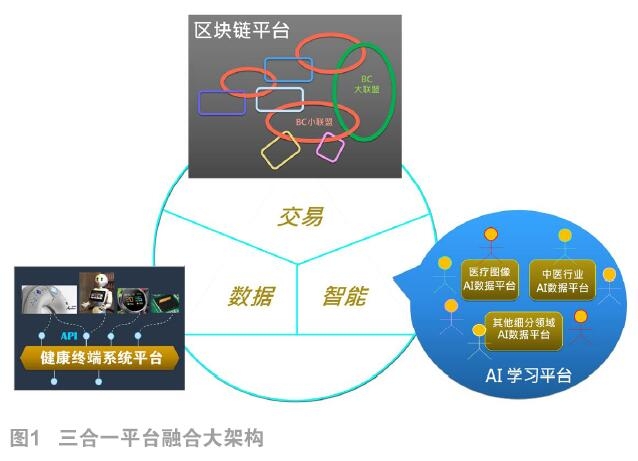

近年来,智能终端平台的大数据汇集,来支撑新兴的AI智慧平台。如果再搭配当今热门的区块链(Block Chain)交易平台,就形成三合一的平台融合大架构了。基于区块链的交易平台、基于智能终端的数据平台、