基于可编程逻辑器件和VHDL语言实现算术逻辑单元的设计-随着可编程逻辑器件的发展,FPGA的应用已经越来越广泛,且用可编程逻辑器件代替传统的普通集成电路已成为一种发展的趋势。可编程逻辑器件FPGA以其高集成度、高速度、开发周期短、稳定性好而受到了人们的青睐,并得到了广泛的应用。由于算术逻辑单元(ALU)在运算中对系统性能要求很高,而采用中小规模的集成电路设计的系统既庞大又存在稳定性的问题。

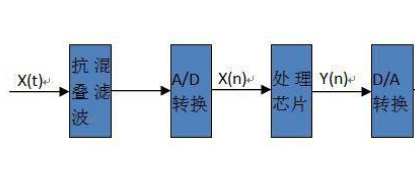

简析DSP的工作原理-DSP内部除了算术逻辑单元(ALU),还包括多个处理单元——辅助寄存器运算单元(ARAU),累加器(ACC),硬件乘法器(MULT),以及丰富的总线资源,它们的存在使得DSP可以拥有一些数字信号处理的特殊DSP指令,以及可以快速的访问存储以及并行操作的能力,保证数字信号处理中的实时的高速度、高精度累加即乘法等运算。

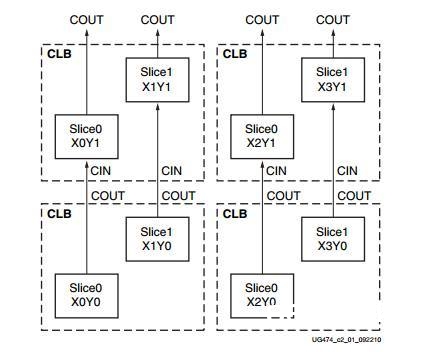

Xilinx FPGA内部体系结构-Xilinx的FPGA的基本结构是一样的,主要由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。

基于管理和组合HDL电路单元IP库的HAD辅助设计软件研究-辅助设计(HAD)软件主要是对HDL语言的电路起一个辅助设计的作用。HAD软件的功能有两个:管理电路单元IP库以及生成所需外围电路的 HDL程序。

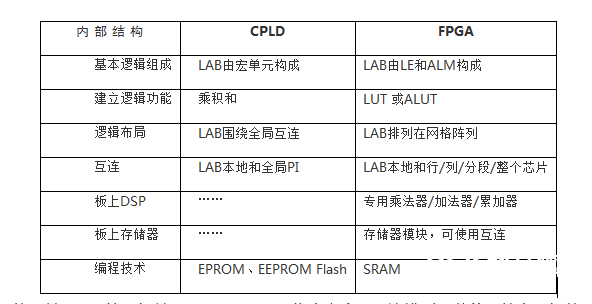

关于FPGA与CPLD之间的区别分析-CPLD主要是由可编程逻辑宏单元(LMC,Logic Macro Cell)围绕中心的可编程互连矩阵单元组成,其中LMC逻辑结构较复杂,并具有复杂的I/O单元互连结构,可由用户根据需要生成特定的电路结构,完成一定的功能。由于CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测的缺点。到90年代,CPLD发展更为迅速,不仅具有电擦除特性,而且出现了边缘扫描及在线可编程等高级特性。较常用的有Xilinx公司的EPLD和Altera公司的CPLD。

fpga介绍_fpga芯片系统结构图-。FPGA芯片主要由7部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。