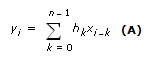

基于电路分割技术的查表法实现根升余弦脉冲成形滤波器FPGA设计-数字通信系统中,基带信号的频谱一般较宽,因此传递前需对信号进行成形处理,以改善其频谱特性,使得在消除码间干扰与达到最佳检测接收的前提下,提高信道的频带利用率。目前,数字系统中常使用的波形成形滤波器有平方根升余弦滤波器、高斯滤波器等。设计方法有卷积法或查表法,其中:卷积法的实现,需要消耗大量的乘法器与加法器,以构成具有一定延时的流水线结构。为降低硬件消耗,文献提出了一种分布式算法(Distributed Arithmetic,DA)的滤波器设计结构。它将传统的乘、累加运算转化为移位、累加运算,当运算数据的字宽较小时,极大地降低了硬件电路的复杂度,提高了响应速度;当运算数据的字长较长时,因其需要更多的移位迭代运算而不适合高速处理的需求。为此,文献提出了采用滤波器的多相结构与改进DA算法相结合的一种设

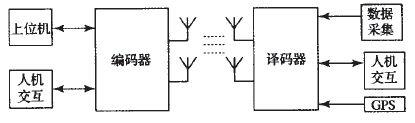

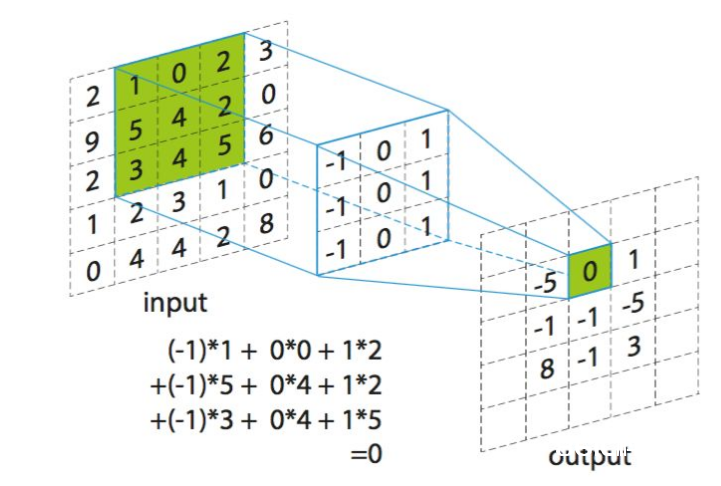

赛灵思FPGA卷积神经网络,云中的机器学习- 人工智能正在经历一场变革,这要得益于机器学习的快速进步。在机器学习领域,人们正对一类名为“深度学习”算法产生浓厚的兴趣,因为这类算法具有出色的大数据集性能。在深度学习中,机器可以在监督或不受监督的方式下从大量数据中学习一项任务。大规模监督式学习已经在图像识别和语音识别等任务中取得巨大成功。

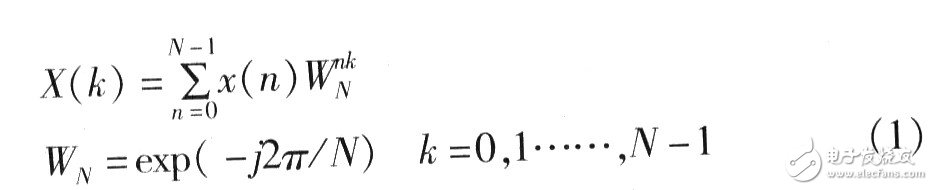

采用FPGA实现FFT算法-随着数字技术的快速发展,数字信号处理已深入到各个学科领域。在数字信号处理中,许多算法如相关、滤波、谱估计、卷积等都可通过转化为离散傅立叶变换(DFT)实现,从而为离散信号分析从理论上提供了变换工具。

一款Xilinx FPGA的CNN加速器IP—AIScale-随着人工智能(AI)的不断发展,它已经从早期的人工特征工程进化到现在可以从海量数据中学习,机器视觉、语音识别以及自然语言处理等领域都取得了重大突破。CNN(Convolutional Neural Network,卷积神经网络)在人工智能领域受到越来越多的青睐,它是深度学习技术中极具代表性的网络结构之一,尤其在图像处理领域取得了很大的成功。