采用VHDL语言实现卷积码编解码器设计-数字信息在有噪信道中传输时,会受到噪声干扰的影响,误码总是不可避免的。为了在已知信噪比的情况下达到一定的误码率指标,在合理设计基带信号,选择调制、解调方式,并采用频域均衡或时域均衡措施的基础上,还应采用差错控制编码等信道编码技术,使误码率进一步降低。

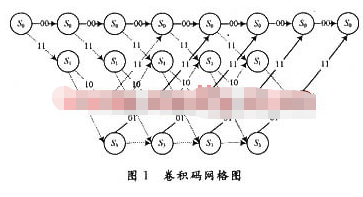

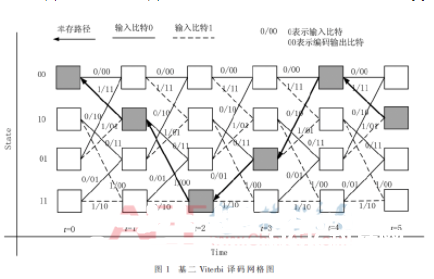

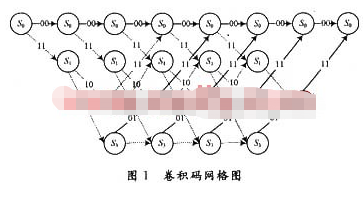

采用可编程逻辑器件的译码器优化实现方案-由于卷积码优良的性能,被广泛应用于深空通信、卫星通信和2G、3G移动通信中。卷积码有三种译码方法:门限译码、概率译码和Viterbi算法,其中Viterbi算法是一种基于网格图的最大似然译码算法,是卷积码的最佳译码方式,具有效率高、速度快等优点。从工程应用角度看,对Viterbi译码器的性能评价指标主要有译码速度、处理时延和资源占用等。本文通过对Viterbi译码算法及卷积码编码网格图特点的分析,提出一种在FPGA设计中,采用全并行结构、判决信息比特与路径信息向量同步存储以及路径度量最小量化的译码器优化实现方案。测试和试验结果表明,该方案与传统的译码算法相比,具有更高的速度、更低的时延和更简单的结构。

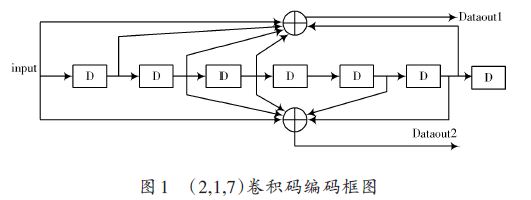

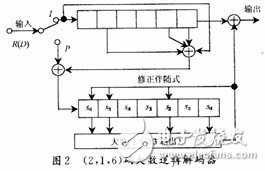

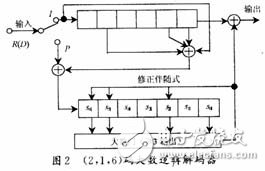

卷积码是一种重要的信道纠错编码方式,其纠错性能通常优于分组码,目前(2,1,6)卷积码已广泛应用于无线通信系统中,Viterbi译码算法能最大限度地发挥卷积码的纠错性能。阐述了802.11b中卷积码的

采用VHDL语言实现卷积码编解码器设计-数字信息在有噪信道中传输时,会受到噪声干扰的影响,误码总是不可避免的。为了在已知信噪比的情况下达到一定的误码率指标,在合理设计基带信号,选择调制、解调方式,并采用频域均衡或时域均衡措施的基础上,还应采用差错控制编码等信道编码技术,使误码率进一步降低。

基于XC6SLX16-2CSG-324型FPGA实现Viterbi译码器的设计-记(n0,k0,m)为卷积码编码器,该编码器共有2k0×m个状态,Viterbi译码器必须具备同样的2k0×m个状态发生器,且每个状态必须有一个存储路径度量值的存储器和一个存储幸存路径信息的存储器,所以Viterbi译码器的复杂度呈2k0×m指数增长。

采用可编程逻辑器件的译码器优化实现方案-由于卷积码优良的性能,被广泛应用于深空通信、卫星通信和2G、3G移动通信中。卷积码有三种译码方法:门限译码、概率译码和Viterbi算法,其中Viterbi算法是一种基于网格图的最大似然译码算法,是卷积码的最佳译码方式,具有效率高、速度快等优点。从工程应用角度看,对Viterbi译码器的性能评价指标主要有译码速度、处理时延和资源占用等。本文通过对Viterbi译码算法及卷积码编码网格图特点的分析,提出一种在FPGA设计中,采用全并行结构、判决信息比特与路径信息向量同步存储以及路径度量最小量化的译码器优化实现方案。测试和试验结果表明,该方案与传统的译码算法相比,具有更高的速度、更低的时延和更简单的结构。