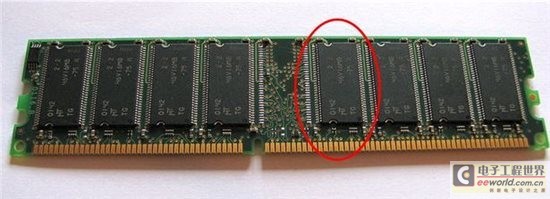

双数据速率同步动态随机存取存储器。哇!真够拗口的。很多人甚至可能都不认识这个全称;它通常缩写为DDR存储器。图1是PC中使用的DDR模块图。在该图中,我在其中一个DDR芯片上画了一个红圈。随着设备日益

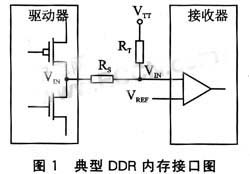

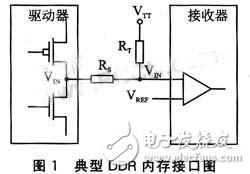

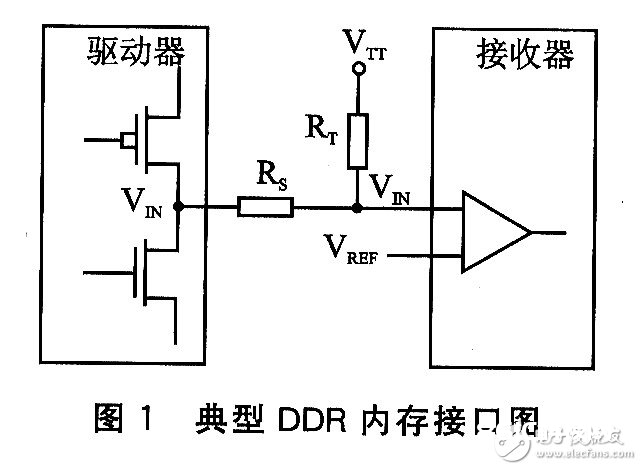

嵌入式DDR布线分析 DDR信号布线介绍-嵌入式 DDR(Double Data Rate,双数据速率)设计是含DDR的 嵌入式 硬件设计中最重要和最核心的部分。随着嵌入式系统的处理能力越来越强大,实现的功能越来越多,系统的工作频率越来越高,DDR的工作频率也逐渐从最低的133 MHz提高到200 MHz,从而实现了更大的系统带宽和更好的性能。

嵌入式DDR总线结构介绍及硬件信号布线分析-嵌入式DDR(Double Data Rate,双数据速率)设计是含DDR的嵌入式硬件设计中最重要和最核心的部分。随着嵌入式系统的处理能力越来越强大,实现的功能越来越多,系统的工作频率越来越高,DDR的工作频率也逐渐从最低的133 MHz提高到200 MHz,从而实现了更大的系统带宽和更好的性能。