FPGA器件的时钟设计-一般情况下,FPGA器件内部的逻辑会在每个时钟周期的上升沿执行一次数据的输入和输出处理,而在两个时钟上升沿的空闲时间里,则可以用于执行各种各样复杂的处理。而一个比较耗时的复杂运算过程,往往无法一个时钟周期完成,便可以切割成几个耗时较小的运算,然后在数个时钟上升沿后输出最终的运算结果。

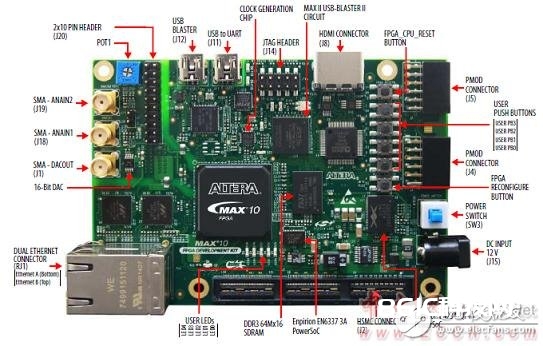

Altera® MAX® 10 FPGA介绍(特性、优势、电路图)-Altera公司的MAX 10器件是单片非易失低成本可编逻辑器件(PLD),具有内部存储可配置的双闪存,用户闪存,集成了ADC,支持单片Nios II软件处理器,主要用在系统管理,I/O扩展,通信控制面板,汽车电子,工业控制和消费类电子产品.本文介绍了Altera MAX 10 FPGA主要优势,Altera MAX 10 FPGA开发套件主要特性,框图,元件分布图,电路图和主要元件表.

可编程逻辑器件改变数字系统设计方法-可编程逻辑器件PLD(Programmable Logic De-vice)是一种数字电路,它可以由用户来进行编程和进行配置,利用它可以解决不同的逻辑设计问题。PLD由基本逻辑门电路、触发器以及内部连接电路构成,利用软件和硬件(编程器)可以对其进行编程,从而实现特定的逻辑功能。可编程逻辑器件自20世纪70年代初期以来经历了从PROM,PLA,PAL,GAL到CPLD和FPGA的发展过程,在结构、工艺、集成度、功能、速度和灵活性方面都有很大的改进和提高。

采用可编辑逻辑器件实现VGA显示系统的设计-VGA(视频图形阵列Video Graphics Array)是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛的应用。

采用CPLD器件XC95288XL-7TQ144I芯片实现Flash读取控制设计-对于Flash,项目中选择了Intel公司的Intel StrataFlash系列的256-Mbit J3型Flash.其数据宽度可分别支持8位或者16位。

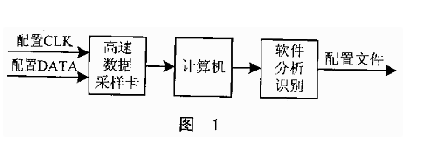

对SRAM工艺的FPGA进行加密的方法浅析-由于大规模高密度可编程逻辑器件多采用SRAM工艺,要求每次上电,对FPGA器件进行重配置,这就使得可以通过监视配置的位数据流,进行克隆设计。因此,在关键、核心设备中,必须采用加密技术保护设计者的知识产权。

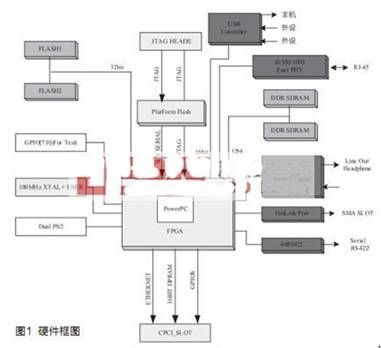

基于Xilinx XC4VFX40系列FPGA器件实现嵌入式系统的应用设计-FPGA是通过逻辑组合电路来实现各种功能的器件。由于FPGA内部集成了大量的逻辑资源和可配置的I/O引脚,加上独特的并行处理架构,可以轻松实现同时对多个外部设备的配置和管理,以及内外各种接口数据的传输。现在开发厂商又在FPGA 内部加入了大量的DSP和Block RAM资源,非常适合图像处理、数字信号处理等运算密集的应用,因此在这些领域取得了广泛的应用。

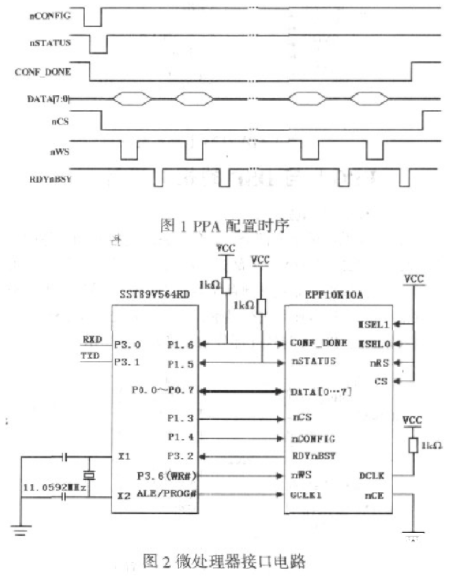

基于SRAM结构的FPGA器件实现快速高效的PPA数据配置-在当今变化的市场环境中,产品是否便于现场升级、便于灵活使用,已成为产品进入市场的关键因素。而基于 SRAM结构的 FPGA器件的出现,为系统设计者动态改变运行电路中的逻辑功能创造了条件,也为现场升级等奠定了基础。但由于 SRAM的掉电易失性,系统每次上电时,必须重新配置数据,只有在数据配置正确的情况下系统才能正常工作。

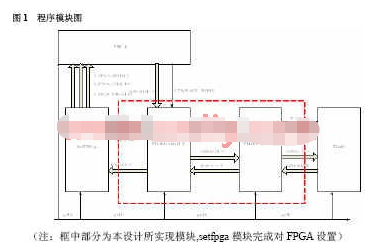

在FPGA中实现嵌入式逻辑分析仪的系统开发与调试应用-嵌入式逻辑分析仪Signal Tap II在对系统硬件模块进行监测时,是将测得的样本数据暂存于目标器件的RAM中,然后通过器件的JTAG端口和Byte Blaster II下载线一起将样本数据信息传出并送入计算机进行数据分析。Signal Tap II允许对设计中所有层次模块的信号进行监测,可以使用多时钟驱动,还能通过设置用以确定前后触发信号信息的比例。其使用方法步骤如下: