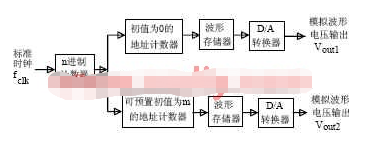

基于FPGA器件和VHDL语言实现波形及移相波形发生器的系统设计-标准时钟(由晶振电路产生)加于进制可编程的n进制计数器,其溢出脉冲加于可预置初值的地址计数器,生成波形存储器所需的地址信号,地址信号的产生频率正比于时钟频率,且周而复始地变化,从而使波形数据存储器输出周期的正弦序列,D/A转换器则输出连续的模拟正弦电压(或电流)波形,如图2所示。

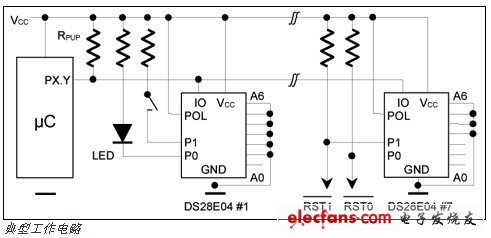

本站为您提供的DS28E04-100 4096位,1-Wire EEPROM芯片,DS28E04-100是具有7个地址输入的4096位,1-Wire® EEPROM芯片。地址输入直接映射到1-Wire 64位器件ID号上,使主机系统能够在多器件1-Wire网络环境中直接识别出DS28E04-100的物理地置和功能。

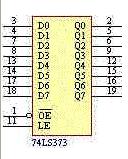

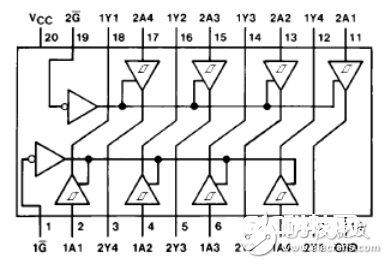

本站为您提供的74ls244中文资料汇总(74ls244引脚图及功能_工作原理及应用电路),本文主要介绍了74ls244中文资料汇总(74ls244引脚图及功能_工作原理及应用电路)。74LS244为3态8位缓冲器,一般用作总线驱动器。74LS244没有锁存的功能。地址锁存器就是一个暂存器,它根据控制信号的状态,将总线上地址代码暂存起来。8086/8088数据和地址总线采用分时复用操作方法,即用同一总线既传输数据又传输地址。当微处理器与存储器交换信号时,首先由CPU发出存储器地址,同时发出允许锁存信号ALE给锁存器,当锁存器接到该信号后将地址/数据总线上的地址锁存在总线上,随后才能传输数据。

本站为您提供的AT24C04/08只读存储器各引脚功能及电压,AT24C04电可檫编程只读存储器

脚号 电压(V) 红笔测(KΩ) 黑笔测(KΩ) 引脚功能

1 5 8.5 14 地址线0

2 0 0 0 地址线1

3 0 0 0 地址线2

4 0 0 0 地

5

本站为您提供的DPTV-3D/dx/ix引脚功能及参数资料,DPTV-3D引脚功能

序号 类型 标识 释义 CPU主接口部分 165-172 I/O AD[T:O] 多路地址和数据线 4 I ADDRESS IC总线地址选择脚 5 I RESET# 系统复位 6 I PS 外部CPU出入使能端 175 I ALE 地址寄存

本站为您提供的IS42G32256-89-PQ存储器各引脚功能,IS42G32256-89-PQ存储器引脚 功能 引脚 功能30-34.47-51 地址数据输入 23.24.56.57 掩膜端口29 数选地址输入 53 定义函数26 列地址选通入 27 行地址选通54 时钟启动 25 写如启动

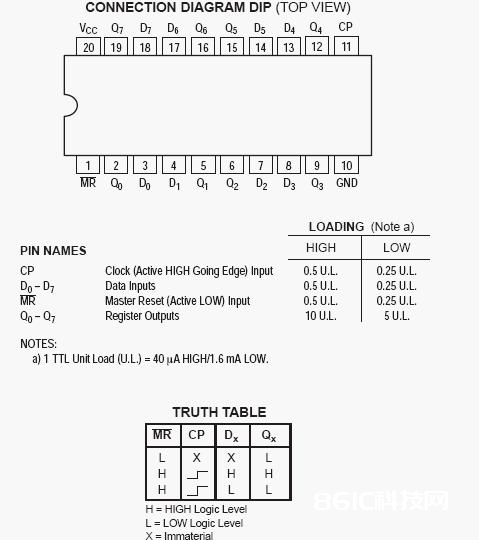

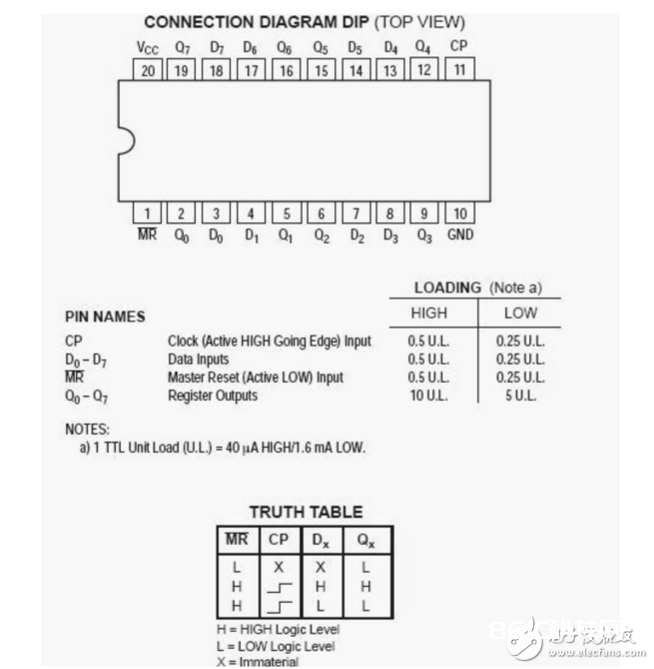

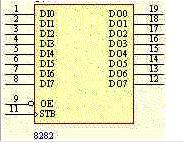

本站为您提供的地址锁存器–8282,地址锁存器–8282

8282是带有三态门的八D锁存器,当使能信号线OE为低电平时,三态门处于导通状态,允许1Q-8Q输出到OUT1-OUT8,当OE端为高电平时,输出三态门断开,输出线OUT1-O