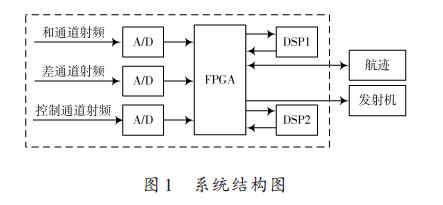

采用FPGA与高性能DSP芯片的雷达信号处理系统设计-现代雷达特别是机载雷达数字信号处理机的特点是输入数据多,工作模式复杂,信息处理量大。因此,在一个实时信号处理系统中,雷达信号处理系统要同时进行高速数据分配、处理和大量的数据交换

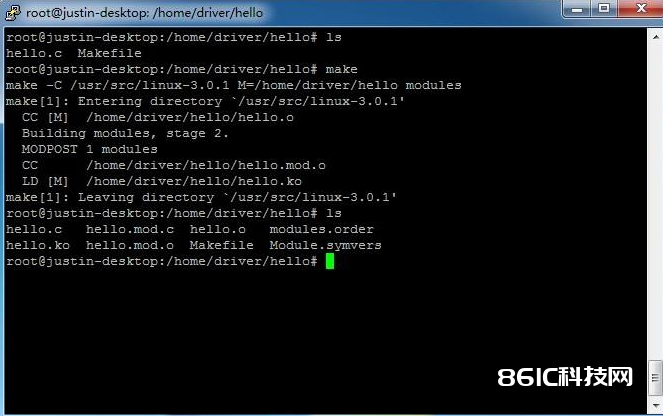

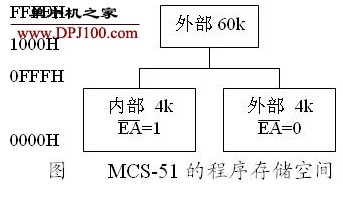

MCS-51单片机位置位复位指令解析-布尔处理功能是MCS-51系列单片机的一个重要特征,这是出于实际应用需要而设置的。布尔变量也即开关变量,它是以位(bit)为单位进行操作的。 在物理结构上,MCS-51单片机有一个布尔处理机,它以进位标志做为累加位,以内部RAM可寻址的128个为存储位。 既然有布尔处理机功能,所以也就有相应的布尔操作指令集,下面我们分别谈论。 位置位复位指令 这些指令对CY及可寻址位进行置位或复位操作,共有四条指令。 CLR C ; 0CY,清CY CLR bit ; 0bit,清某一位

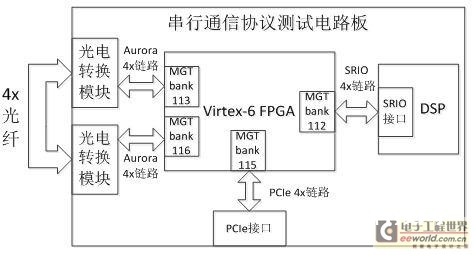

在高性能雷达信号处理机研制中,高速串行总线正逐步取代并行总线。业界广泛使用的Xilinx公司Virtex-6系列FPGA支持多种高速串行通信协议,本文针对其中较为常用的Aurora8B/10B和PCI

针对数字电路系统设计中存在的信号完整性、散热、电磁兼容性(EMC)等问题,结合HyperLynx仿真软件提出了一种综合仿真方法。通过雷达信号处理机的设计实例,详细描述了HyperLynx各仿真模块的功