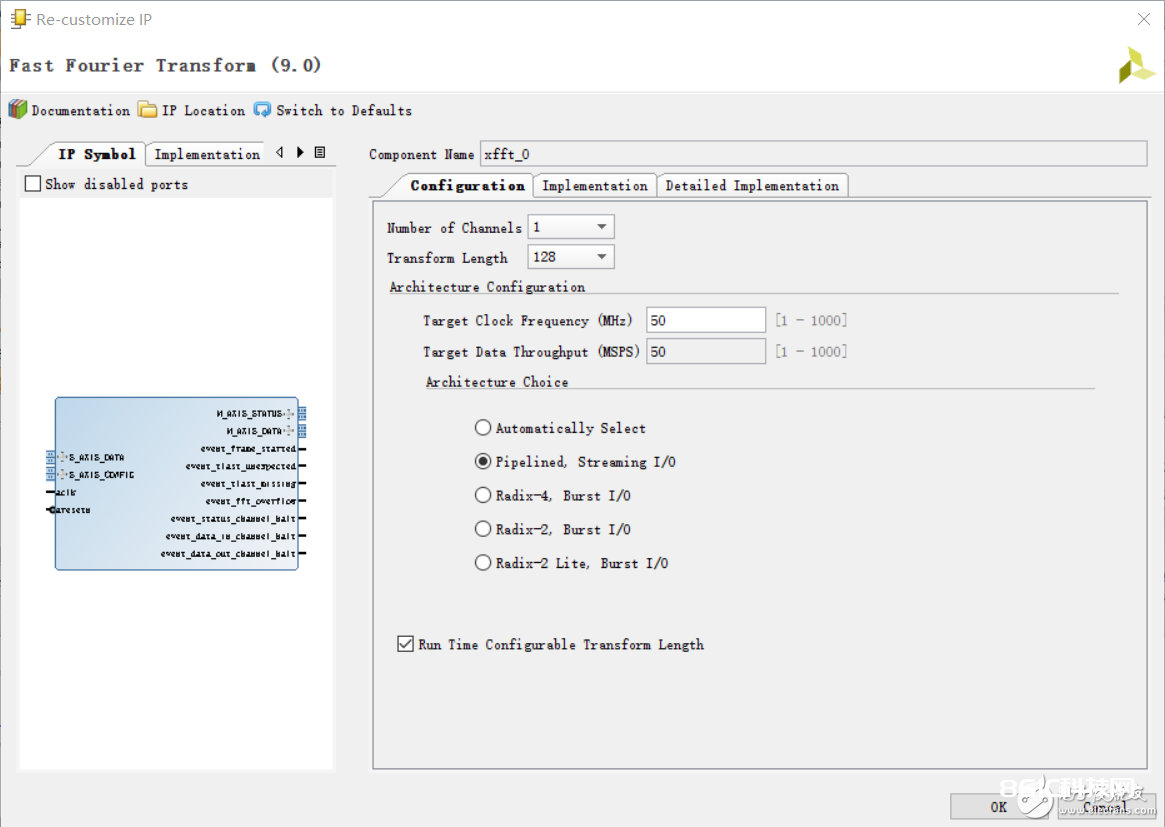

通过Xilinx FFT IP核的使用实现OFDM-由于OFDM接收机中大多是数据串并转换后的连续低速并行数据流输入FFT,故这里采用流水线结构。之后根据OFDM子载波数选择变换长度。该IP核仅支持50MHZ采样率数据的流水线处理,如果数高速通信场合,可以再次将数据串并转换用多个FFT IP核并行运算,也就是FPGA设计中常用的“面积换速度”。

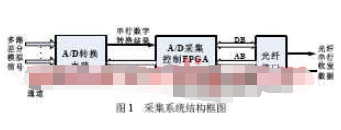

基于FPGA XC3S400芯片和ARM相结合实现数据采集系统的设计-在往复式压缩机状态在线监测系统中,由于压缩机结构复杂、零部件多、运动形式各不相同,发生的故障也就会多种多样,因此需要对各个部件的多个测点的模拟信号进行实时数据采集,同时还要对一些测点周围不同的位置的信号进行同步采集,这就对信号采集的同步性有严格的要求。

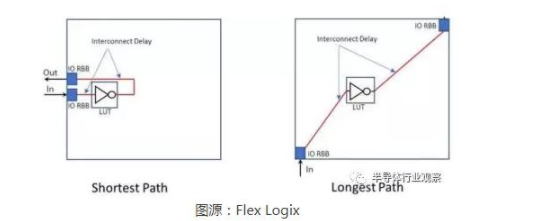

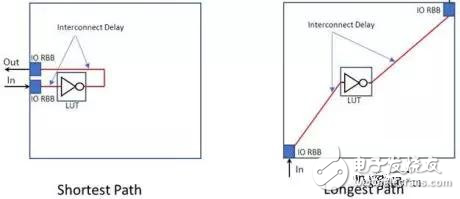

关于eFPGA性能分析和SoC架构师的分析介绍-嵌入式FPGA(eFPGA)是指将一个或多个FPGA以IP的形式嵌入ASIC,ASSP或SoC等芯片中。 换句话说,eFPGA是一种数字可重构结构,由可编程互连中的可编程逻辑组成,通常表现为矩形阵列,数据输入和输出位于边缘周围。 eFPGA通常具有数百或数千个输入和输出,可连接到总线、数据路径、控制路径、GPIO、PHY或任何需要的器件。 所有eFPGA都将查找表(LUT)作为基本构建模块。 LUT有N个输入选择一个小表,其输出表示N个输入的任何需要的布尔函数。

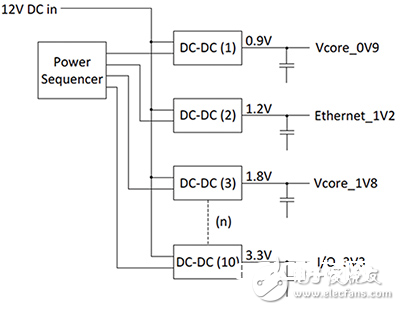

关于设计FPGA系统中有源电容放电电路的方法和需要注意的问题-电信设备,服务器和数据中心的最新FPGA具有多个电源轨,需要正确排序才能安全地为这些系统上下供电。高可靠性DC-DC稳压器和FPGA电源管理的设计人员需要一种简单的方法来安全地放电大容量电容器,以避免损坏系统。 FPGA电源排序 最新在生成片上系统FPGA的过程中,它们可以提供十个独立的电源轨,为Vcore,存储器总线电源,I/O控制器,以太网等提供电源。

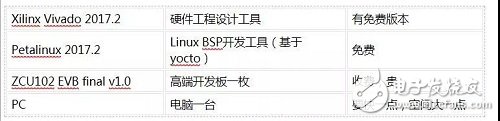

Zynq UltraScale+ MPSoC 上的多个Linux UIO设计-本实验工程将介绍如何利在赛灵思异构多处理器产品系列 Zynq UtralScale+ MPSoC ZCU102 嵌入式评估板上实现多个 UIO,同时借助赛灵思的工具完成硬件工程和 linux BSP 的开发,最后通过测试应用程序完成测试。

采用DSP实现H.324可视电话系统设计-以PC机为平台,利用现有的声卡、视频要集卡和调制解调器作为输入和输出设备,采和基于WINDOWS的多线程技术软件实现H.263视频器、解码/发送、接收、显示等多个任务。在实际应用系统时需要考虑到PC的处理能力、与接收端的连接和相应的图像格式等问题,可以在编码模块中采用汇编语言,提高执行速度,并引入MMX技术,进一步提高执行速度。它的特点是成本低、配置少,便于移植和升级,但对计算机的处理能力、编解码的算法速率的要求比较高,一般难于达到实时要求。

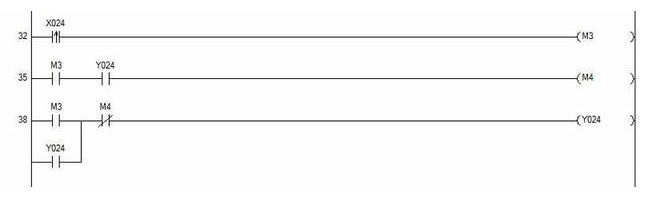

采用FPGA器件控制ADC和数据传输实现数据采集系统的设计-数据采集系统是计算机测控系统中不可或缺的组成部分,是影响测控系统的精度等性能指标的关键因素之一。常用数据采集方案是以微处理器为核心控制多个通道的信号采集、预处理、存储和传输,即用软件实现数据的采集,这在一定程度上局限了数据采集的速度、效率及时序的精确控制。